这是一道 HDLBits 上面的题目(Probelm 97 Dual-edge triggered flip-flop)。

目的是实现一个带双边沿检测的触发器。我们知道,FPGA上是没有带双边沿检测的触发器的,即不存在这样的写法:

always @(posedge clk or negedge clk)

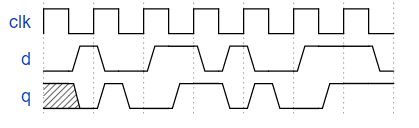

哪怕写了,没有这样的资源也实现不了,无法综合。那么我们怎么通过硬件电路设计去实现下面的时序图呢?

题目也给出了相应的提示:我们可以同时实现对时钟上升沿和下降沿的检测,然后通过某种方式进行组合。

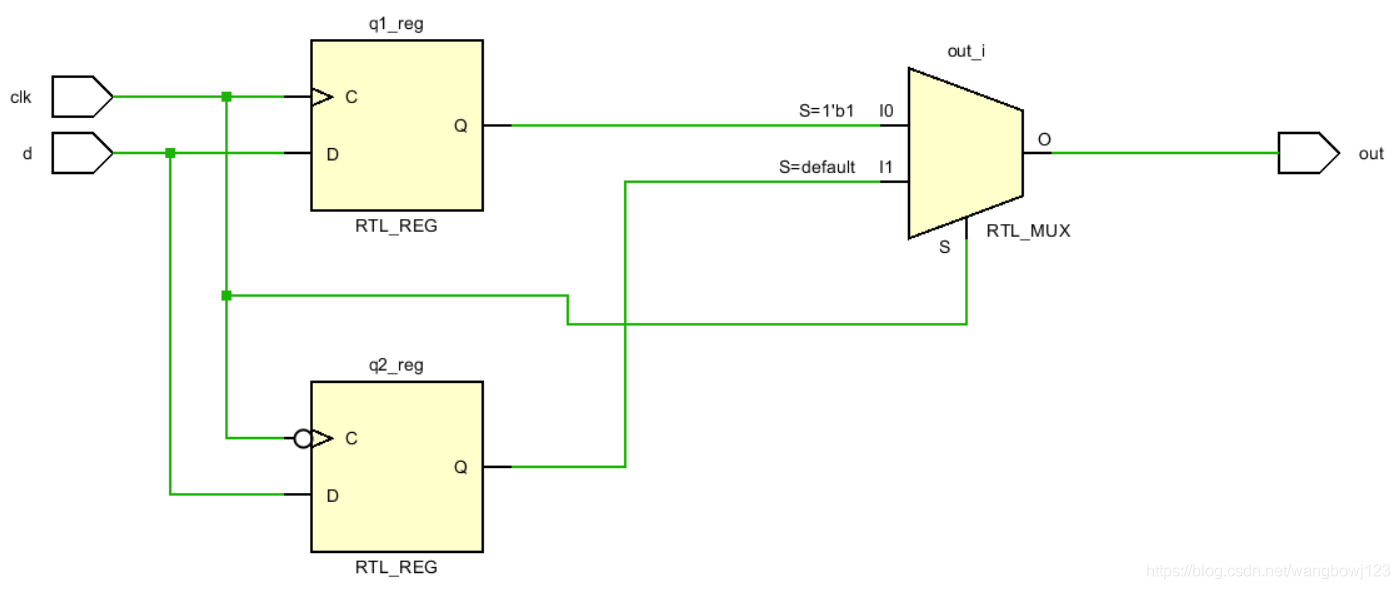

下面给出一种通过多路复用选择器实现的方法。

`timescale 1ns / 1ps

module test(

input clk,

input d,

output out

// output cout

);

reg q1, q2;

assign out = clk ? q1 : q2;

always@(posedge clk)

begin

q1 <= d;

end

always@(negedge clk)

begin

q2 <= d;

end

endmodule

电路如下:

即通过分别实现对上升沿和下降沿的检测,并用 Mux 根据 clk 进行选择从而得到既可以检测上升沿也可以检测下降沿的触发器功能。

还有一种基于异或运算进行。我们知道任何一个数异或一个数再异或同一个数,将得到本身。这就是最简单的加密与解密原理。

module top_module(

input clk,

input d,

output q);

reg p, n;

// clk的上升沿

always @(posedge clk)

p <= d ^ n;

// clk的下降沿

always @(negedge clk)

n <= d ^ p;

//在上升沿时候,p=d^n, 则q=d^n^n=d;

//在下降沿时候,n=d^p, 则q=p^d^p=d;

//加载一个新值时会取消旧值。

assign q = p ^ n;

endmodule

电路如下:

版权声明:本文为wangbowj123原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。