数据加扰器的实现

背景:

当输入的信号出现连续的 0 或连续的 1 时候,接收端容易出现判决错误,避免这种情况,在不增加冗余情况下,通过扰码器使原始信息生成具有白噪声特性的随机序列。

扰码原理:

数字通信中, 若经常出现长的 0 或 1 序列,将会影响位同步的建立和保持。在发射机使用扰码,可以避免这种数据对于接收机定时的不利影响。同时,为了限制电路中存在的不同程度的非线性特性对其他电路通信造成的串扰,要求数字信号的最小周期足够长。将数字信号变换成为具有近似白噪声统计特性的数字序列即可满足要求,这通常用加扰来实现。

来源:

802.11a 18.3.5.5 PLCP DATA scrambler and descrambler :

由SERVICE、PSDU、tial和pad部分组成的DATA字段需要用长度为127的帧同步扰频器进行置乱。PSDU的八位被放置在传输串行比特流中,第0位在前,第7位在后。帧同步扰频器使用的生成器多项式S(x)如下所示

在ofdm系统data域数据的处理中, 首先需要进行加扰操作。Data域由service域, psdu, 尾比特(不需要加扰), 填充比特构成,并用一个长度为 127 位的加扰器进行加扰。 Psdu 的八位数据按发送串行比特流形式进行, 0 比特在前, 7 比特在后,当初始状态全为 1 时,加扰器循环产生的 127 比特序列为 00001110 11110010 11001001 00000010 00100110 00101110 10110110 00001100 11010100 11100111 10110100 00101010 11111010 01010001 10111000 1111111。加扰发送数据和解扰接受数据使用同一个加扰器。发送时,加扰器初始状态设置为伪随机非零态。为了能估计接收端解扰器的初始化状态,在加扰前, service 域的 7 个低有效比特置 0, 使得接收端可以识别出加扰器的初始伪随机数列。

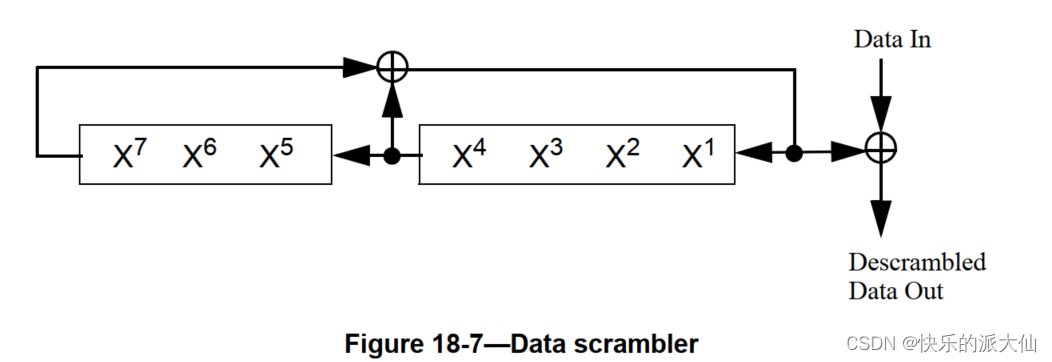

帧同步扰码器结构

由这个加扰器的构造,我们就可以知道这实际是一个

移位寄存器

,输出是一个

x7与x4的异或

,然后这个值再与我们的输入数据异或,这就是我们加扰之后的数据

Verilog代码:

移位寄存器的实现:

///shift reister scramble register

always @(posedge clk_Modulation or negedge reset) begin

if (reset == 1'b1) begin

h1 <= scramble_int;

end else if(scramble_bit_valid_end_flag == 1'b1) begin

h1 <= scramble_int;

end

else if (data_bit_valid == 1'b1) begin

h1 <= {h1[5:0],h1[6]^h1[3]};

end

end为了优化时序,这里将输出单独输出:就是将异或单独输出

实现代码如下:这是是从0开始计数,所以是x6 ^x3;

//h2 scramble register output r3^r6

always @(posedge clk_Modulation or negedge reset) begin

if (reset == 1'b1) begin

h2 <= 1'b0;

end else if(scramble_bit_valid_end_flag == 1'b1) begin

h2 <= 1'b0;

end else if (data_bit_valid == 1'b1) begin

h2 <= h1[3]^h1[6];

end

end