最近在布Blackfin视觉的板子,开始看了一些高速板的资料,感觉收获挺大的。贴些东西来。

我看了些资料,主要是一篇叫High-Speed Digital System Design的文章,PCBBBS(

www.pcbbbs.com

)的大侠们翻译的。可以从

http://www.pcbbbs.com/dispbbs.asp?boardID=4&ID=122837&page=1

下载到。如果这个链接失效了,请从PCBBBS首页进,分支路线为:“中国PCB论坛网 → 线路设计 → SI高速设计 → 帖子列表”,搜索High-Speed Digital System Design。

其实我也是刚入门,本文的作用仅仅是给大家提供入门级HOWTO:

什么样的板子需要考虑高速所造成的效应?用数字信号的上升时间来衡量,任何长度超过信号在其上升时间内走过距离的十分之一的导线都必须考虑所谓的“传输线效应”。说形象的,如果是133MHz的SDRAM(前几年最常见的PC133SDRAM内存条上的芯片,上升时间1ns),15mm以上距离,就必须考虑传输线效应。这个距离怎么计算出来的呢,如果你算算,实际上电磁波在100ps里能够走上30mm呢,怎么是15mm呢?实际上电信号在导体中的速度和导体周围的介质有关,公式为(BLOG没法写公式,我按照MATLAB符号数学格式写了)v=c/sqrt(Er),c是光速,Er是导线周围导体的介电常数,一般电路板使用一种叫FR4的玻璃纤维,Er=4.X。好的,当你知道你所要面对的情况之后请仔细阅读我上面提到的这个文章。

对于实际引用,我们会遇到以下3个问题:

1.布线问题,怎么在我们熟知的PCB设计软件中解决

2.阻抗匹配,这个词很经常听到啊,举例来说明吧。请你找一根杂牌的示波器探针线,测量数字电路管脚输出的波形,也许你会看到方波边沿出现了过冲,这有部分是因为探针的阻抗和芯片、示波器输入阻抗不匹配造成的。这个需要你阅读文章了,实际上完全匹配是不可能的,问题是怎样将阻抗不匹配造成的影响减少到最小。

3.仿真问题,怎么样验证自己对电路板进行的修改是正确的

问题2,我目前也没有整太明白,这个需要看的书更多。我上面提供的材料里就有一些简单的描述。

问题1,我用的是Altium Designer 6.5,就是大家所熟知的Protel,后来又叫DXP,再后来就叫了Altium Designer。打开菜单Design>Rules,里面的High Speed和Signal Integrity是管高速布线的,大家可以找相关的书解决。

这里我提个我用到的,SDRAM地址/控制和数据线分组等长问题的解决。以Altium Designer 6.5为例(其实Protel 99se也差不多,DXP就更不用说了)。首先Design>Netlist>Edit Nets,新建SDRAM_AC(地址和控制)和SDRAM_D(数据)两个Netclass,把相应的Net添加进来,Design>Rules,选择High Speed>Matched Net Length>新建两个规则SDRAM_AC和SDRAM_D,在Where the first object matches里选择Net Class,然后分别选中刚才建立的两个Net Class。下面的Constraints是最神奇的蛇形线规则设置(电脑主板上经常可以见到的那些弯弯曲曲的绕着走的线,目的就是让短的线绕着走,增加长度以和长线匹配),Tolerance是同组线长最大差距值,我设的是7.62mm,就是0.3inch,具体数值有的强人可以控制在正负50mil以内,由于我们同学有做10mm成功的例子,我放弃了50mil的想法。Style是蛇形线的风格,可以选着玩玩看看,其他的设置可以自己试,决定了蛇形线的形状。这些规则是为了自动生成蛇形线准备的,鉴于自动生成糟糕的结果,我不建议这么做。这些规则仅仅是用来进行DRC(Design Rule Check,在Tools菜单中的命令)的。另外告诉大家怎么自动生成,菜单Tools>Equalize Net Length,注意这个命令:1、仅仅对头尾都连接上的线起作用即针对Routed Nets,2、如果板子太密没有生成蛇形线的地方,执行后没有反应,你可以修改Rules来缩小蛇形线的尺寸看看,3、可以多次调用这个命令,使线长逐步趋于一致,4、如果同组线本身走线长度差距太大,或者你的要求太高(哈哈50mil),那么可能会存在永远也没有办法一致长度的线,这个在执行命令后生成报告中会告诉你。

说说手动怎么做(仅仅针对DXP以上版本),右下角的弹出菜单站里点PCB>PCB,你可以看到你刚才设置的Net Class,选中后可以看到每个Net(无论是Routed还是Unrouted的)长度,在布线时注意调整,如果出现了长度差距太大的线,可以在短线周围预留空间,手工用圆弧连接的方法画出蛇形线。

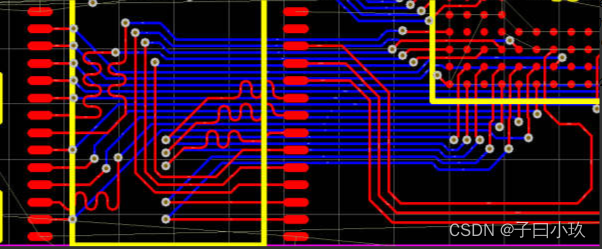

贴个图看看,你可以先画一个图中那样的波浪形状,然后Ctrl+C和Ctrl+V。当然PADs好像做这个更加专业,但是我看同学用的好像没有Altium Designer操作这么方便。

问题3,我没有做太深入的研究,随便找了个软件HyperLynx 7.5,哈哈原因很单纯,因为Altium Designer可以直接把PCB存成HyperLynx格式的,其实PADs里带的就是HyperLynx。随便说下,HyperLynx作PCB分析需要几个东西:1、PCB图(废话,哈哈);2、电路中用到的元件的仿真模型,这个可以在器件厂商的主页上面找到,如SDRAM的厂家Micron(

www.micron.com

),如果没有模型也可以根据器件的DATASHEET自己做,这个可是高级操作;器件模型里规定了器件的管脚输入输出阻抗等一系列的参数;3、电路板的参数,比如板厚、铜厚、多层板每层间距离、介电常数等,这个需要问你委托加工电路板的厂家。简单仿真步骤如下:1、PCB,Altium Designer可以生成,但是一些细节参数可能会错,需要修改下,一般HyperLynx也会自动修改,菜单Edit>Stackup可以修改并输入从电路板制造商那儿得到的数据,2、仿真模型,Edit菜单中的.Ref IC Automapping file等指令就是用来映射器件和模型的,可以尝试下就知道了,操作很简单,3、开始仿真,菜单Simulate>Run interactive simulation就可以看到电信号上升和下降时输入和输出管脚波形的变化了。另外,Report菜单里的Net Statistics可以看到选中Net的特征阻抗等数据。详细的操作请阅读相关书籍。

正如我开始说的,在SI(Signal Integrity)方面,我也是新手,希望有大虾看到后对我的文章予以斧正。

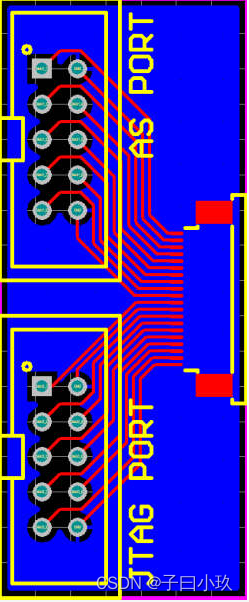

刚开始的时候我一直想知道,电路板仿真软件到底是什么样子的,能看到什么样的方针结果,为了给和我一样的菜鸟一个直观的印象,我再贴个仿真过程图解,本例使用HyperLynx 7.5,如图这样一个简单的PCB,用来转接直插的FPGA配置接头到FPC软线插座,顶层线路底层地。

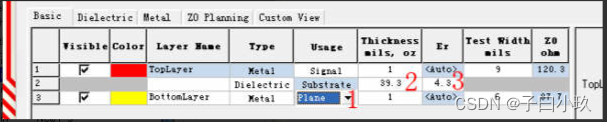

先将其另存为HyperLynx可以打开的文件,在Altium Designer中,菜单File>Save as,然后选择保存类型为Export HyperLynx,确认。在HyperLynx中,菜单File>Open Boardsim Board,选择刚才保存的文件,有Warning先OK,然后菜单Edit>Stackup,设定板厚,介电常数等基本参数,如图所示:1、修改底层为参考平面,事实上仿真需要一个参考平面,否则无法进行,很抱歉,我是新手不知道双层的没有地平面的板子该怎么仿真。2、修改板厚,此板1.0mm厚。3、按照电路板制造商给你的介电常数设置Er。

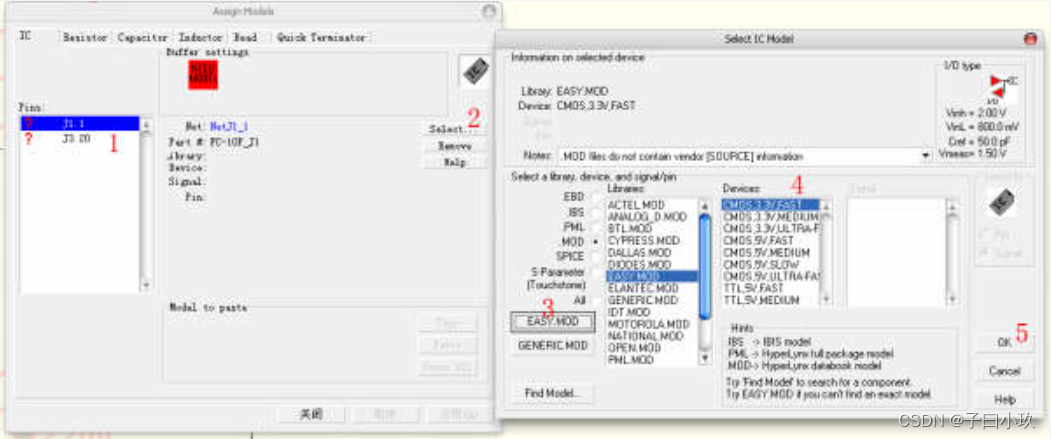

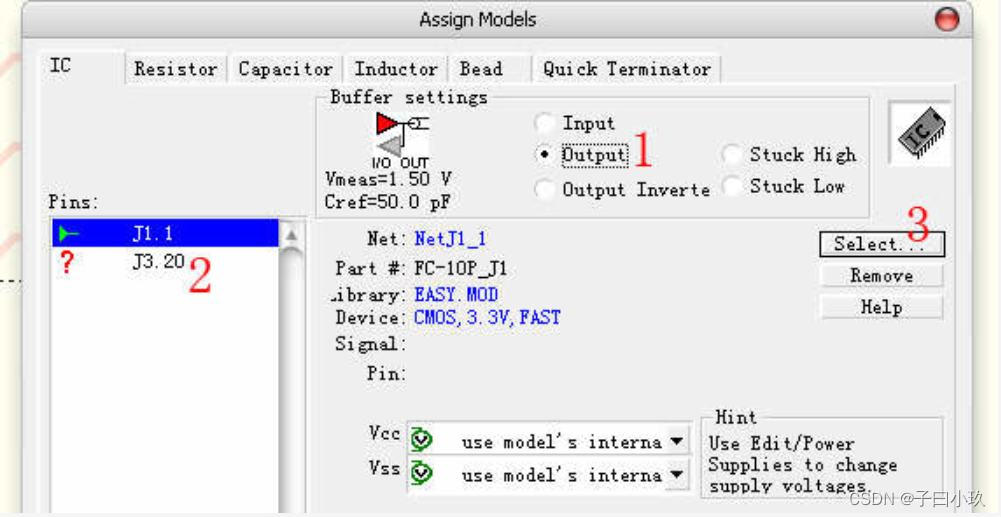

接下来设定Net的输入输出属性,选择一个Net,菜单Select>Net by Name,随便选择一个Net,点确定,如图所示

然后菜单Select>Component Models or Edit Values,弹出的窗口里选Select,然后点EASY.MOD,再选CMOS,3.3V,FAST(这仅仅是个演示,实际要选择与Net相对应的器件,可以点Find Model按钮)

接下来Assign Models窗口中的内容变了,先将Pin J1.1配置为Output,然后再选择Pin J3.20做一次同样的选择过程,将J3.20配置为CMOS,3.3V,FAST(当然实际上不是),方向为Input,然后就可以进行仿真了。

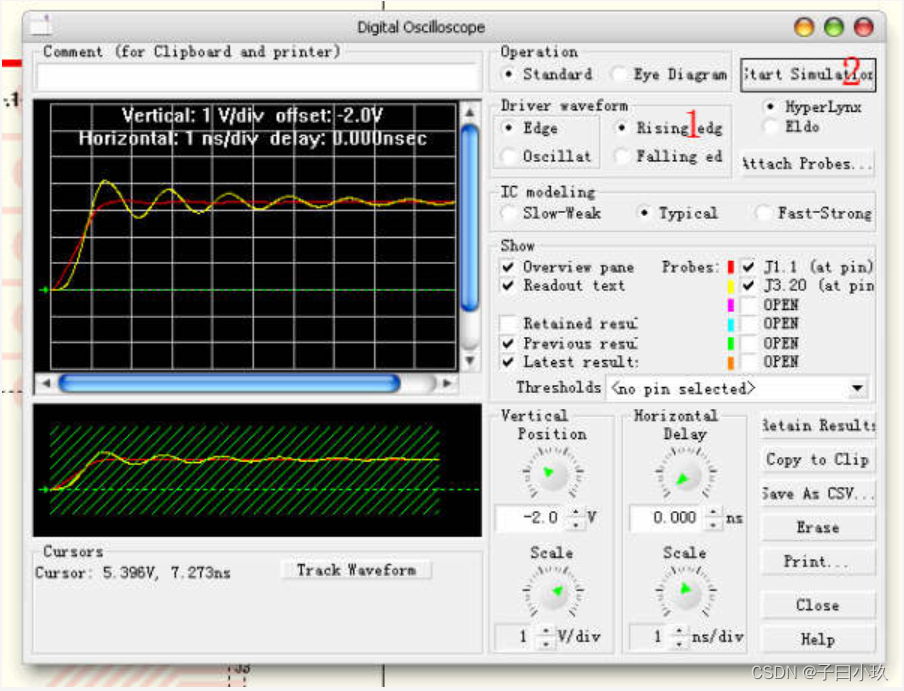

菜单Simulate>Run Interactive Simulation,例如要看一个上升沿在这个线上传输的效果,在Driver waveform里选择Rising edge,然后点Start Simulation,在左边的示波窗口里就可以看见波形了。黄线是经过传输后的波形,由于阻抗不匹配出现了振铃现象。

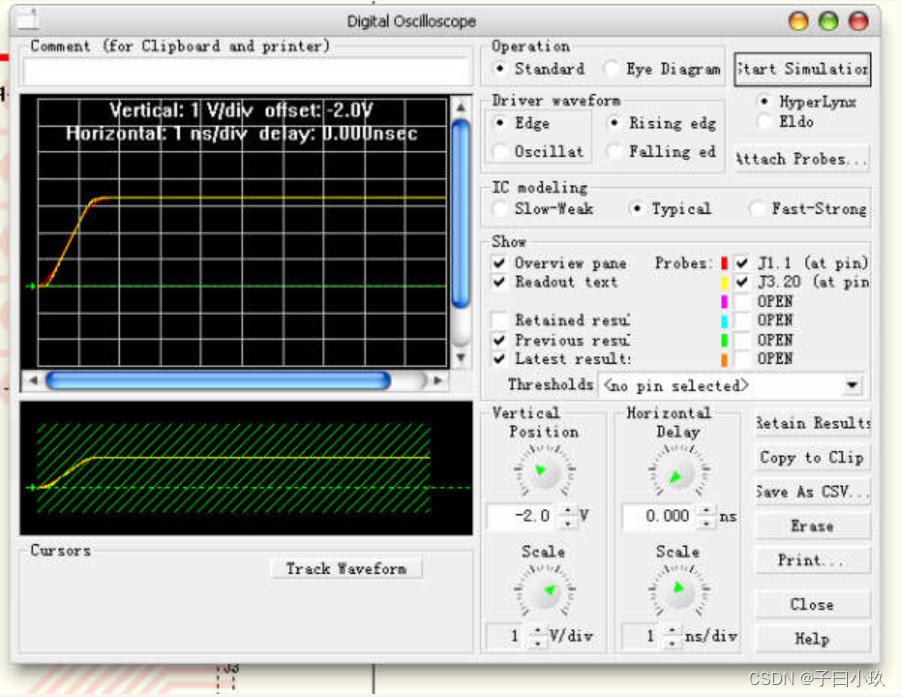

那么传输线阻抗匹配的怎么实现呢,波形又是什么样的呢?我们可以用菜单Reports>Net Statistics找到传输线的特性阻抗Z0,此时Z0是120.3欧姆。而通过查找Pin J1.1的模型可以发现输出阻抗为5欧姆(操作命令为Select>Component Models or Edit Values,在弹出窗口中选择Edit Model File按钮,就可以看见输出阻抗),根据传输线原理要消除振铃,可以进行源匹配、负载匹配等,简单点说就是在导线上串联或者并联电阻,阻止信号反弹的发生,具体细节请看我上面推荐的文章。为了看看匹配的效果,这里我来个变态的,直接修改传输线本身的属性——这在实际中是不可选的操作。菜单Edit>Stackup,将板厚修改为0.27mil,此时计算出的传输线特征阻抗恰好是5欧姆,再来看仿真

哈哈,这回的结果不错了吧,这就是阻抗匹配的作用。其实你可以仔细观察电脑主板的内存条边上,有很多的贴片阻排,就是用来匹配传输线阻抗的。今天就到这里。