目录

2. Quartus使用Vscode作为文本编辑器的配置过程

3. Vscode自动检查Verilog/VHDL语法错误的配置过程

1. Vivado使用Vscode作为文本编辑器的配置过程

Vivado的Tool菜单中,打开Settings

按照下图选

按照下图选

输入: C:/……/Microsoft VS Code/Code.exe -g [file name]:[line number]

即:vsCode绝对路径 -g [file name]:[line number]

2. Quartus使用Vscode作为文本编辑器的配置过程

按照下图选

按照下图填

输入: “C:\ ……\Microsoft VS Code\Code.exe” -r -g -n%l %f

即:vsCode绝对路径-r -g -n%l %f

3. Vscode自动检查Verilog/VHDL语法错误的配置过程

Vscode安装Verilog-HDL/SystemVerilog插件。插件功能:语法高亮、自动补齐、列出端口。

使用Vscode实现自动语法纠错,实现这一功能的前提是vivado安装目录下的xvlog,需要将这个工具所在的目录放置在系统的环境变量,以便VsCode能够方便的调用他。具体的目录就是Vivado的bin文件夹。

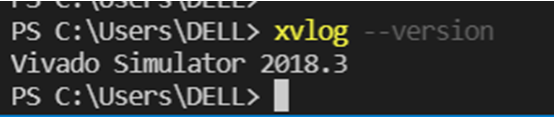

重新启动Vscode之后,在Vscode终端中输入xvlog –version 检测是否生效。

如果没有打印出未找到该命令,重启电脑试试。

接下来我们在设置里,找到刚才安装的verilog扩展,将verilog的Linter更换成xvlog。

同理,如果想使用的语法纠错插件来自modelsim,quatus,选择他们对应的linter即可。各个软件的语法排错机制还是有一点细微的不同的,建议选择正确的解析器。设置完成之后,就能实现语法的纠错了。

需要注意的是,编译器需要手动保存之后,才会开启xvlog解析,也就是说观看最新错误之前,需要保存一下。

4. 自动生成Testbench

首先保证电脑中安装了Python

安装Verilog_Testbench插件

下载 安装chardet(chardet检测编码非常容易,chardet支持检测中文、日文、韩文等多种语言。)

下载地址:官网:

chardet

:

chardet · PyPI

再按如下步骤安装:

第一步:下载压缩文件,例如: ‘chardet-4.0.0.tar.gz’;

第二步:解压文件到python安装位置下的‘site-packages’目录下,例如:‘C:\Users\DELL\AppData\Local\Programs\Python\Python38\Lib\site-packages’;

第三步:win+r输入cmd打开终端命令窗口,cd C:\Users\DELL\AppData\Local\Programs\Python\Python38\Lib\site-packages\chardet-4.0.0进入解压的‘chardet-4.0.0’目录下,执行命令:python setup.py install ,即可安装

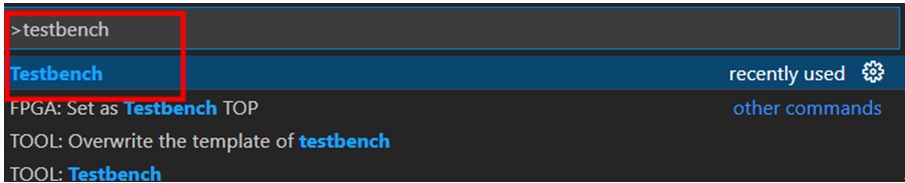

在Vscode中按ctrl+shift+p,输入testbench,在命令行就会自动输出Testbench代码了

复制粘贴即可使用。

5. Vscode实现定义跳转

下载最新版ctags,旧版的有些功能不够齐全。将下载的压缩包解压后放到某个不经常挪动的文件夹中。下载ctags地址:

https://github.com/universal-ctags/ctags-win32/releases/tag/2021-10-20%2Fp5.9.20211017.0-4-gdf3e2f58

将ctags.exe的路径设置到系统环境变量中。方法和xvlog一样,将ctgas下载好解压后将其路径添加到系统环境变量中

添加路径后检查设置里是否已经将ctags添加到工具中

重启VSCode

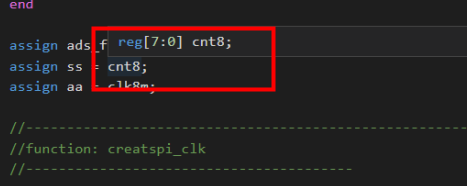

效果:鼠标放在信号上,就会有声明显示在悬浮框中

Ctrl+左键,点击信号名,自动跳转到声明处

光标放在信号处,右键选择查看定义,可以在此处展开声明处的代码,用于修改声明十分方便,就不用再来回跳转了,再按ESC,关闭。

到此就配置成功。

6. Vscode码FPGA代码常用插件

插件:Bracket Pair Colorizer 2插件,让你的括号变得更漂亮(不过case-endcase这个bug貌似还有)

插件:VHDL插件,支持VHDL关键字高亮显示。

插件:TerosHDL插件,非常NB的插件。支持VHDL关键字高亮显示。支持状态机、原理图、报告一键生成

具体功能用法请看:https://terostechnology.github.io/terosHDLdoc/