目录

FPGA设计流程

设计规划

- 明确工程要实现的功能:点亮LED灯

- 了解工程设计的硬件资源:按键和灯

- 创建文件夹

波形绘制

创建Visio文件

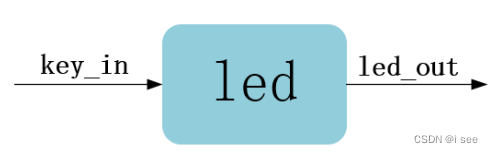

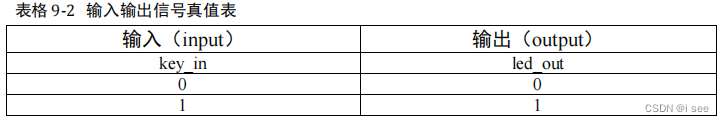

- 对项目的系统结构和层次进行设计:实现该功能所需的模块(LED模块)、系统的输入输出是什么(key_In和led_out):

- 波形设计:根据真值表绘制出波形:

代码编写

用Quartus新建工程

-

设置位置/文件名——>添加已经写好的.v文件——>选择芯片类型——>

选择第三方的开发工具

-

选择芯片类型:

- 选择使用哪个系列的芯片:CycloneIV 系类

-

选择该芯片的封装类型:FBGA

封装

-

管脚数量:256

-

速度等级:8

-

芯片具体型号:EP4CE10F17C8

RTL代码编写

- 在rtl文件夹下创建led.txt,将后缀改为.v ,用notepad++编写代码

- quartus添加代码文件

- 代码的分析和综合,点击start analyze & synthesis

![]()

RTL视图的查看

- 找到Compile > Analysis & Synthesis > Netlist Viewer > RTL Viewer 并双击

![]()

结果与预计表达一样

逻辑仿真

验证代码设计的正确性

- 编写Testbench测试脚本:在sim文件夹下创建tb_led.txt,将后缀改为.v,用notepad++编写代码,编写完成后,添加到quartus项目文件中

仿真设置

-

首先打开上方菜单栏“Assignments

”下的“

Setting…”,选择“

EDA Tool Settings”下的“Simulation”,中“

Tool name:

”栏选择“

ModelSim

”,其余默认(根据实际需求修改)

设置NativeLink

-

“

NativeLink setting:

”的“

Comple test bench”,点击后面的“

Test Benches…

”,点击“New”,设置名称”tb_led”,结束仿真时间1us,文件名“tb_led.v”,点OK,完成NativeLink的设置。

打开ModelSim观察波形

-

在Quartus软件中点击“Toos”下的“Run Simulation Tool

”下的“

RTL Simulaton

”打开

ModelSim

进行功能仿真。

ModelSim的基础用法见书151。

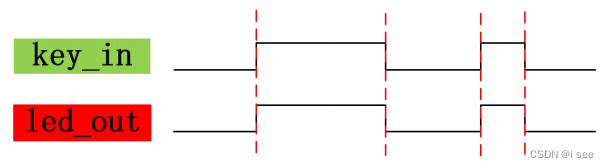

波形对比

仿真波形分析

-

将ModelSim 仿真出来的波形图和之前用根据自己理解用 Visio 画出来的波形图进行对比。

绑定管脚

打开管脚绑定界面

![]()

-

约束方法: 一 种是在的 “ Location” 列“

key_in

” 行输 入“

M2

”, 在 “led_out

”行输入“L7”;

另一种方法是直接鼠标左键按住信号的名字,将其拖动到需要绑定的管脚上即可。

全编译

管脚绑定后就可以对全局进行布局布线了,点击全编译

![]()

通过

JTAG

将网表下载到开发板(add “sof”文件)

-

线路正确连接后,打开开关为板卡上电

-

打开下载界面

![]()

- 硬件连接设置:“No Hardware”即没有连接到硬件,选择接的硬件是USB-Blaster,点击 “Hardware Setup…”,在弹出的界面中的“Currently selected hardware:”选择“USB-Blaster[USB-0]”

-

下载的方式:选择“JTAG

”下载模式

-

add files,把quartus_prj\output_files里的.sof文件添加进去

-

点击start

固化程序

生成.jic文件

-

点击菜单栏“

File

”下的“

Convert Programming Files…

”

-

“

Programming file type:

”栏是选择输出文件的类型,选择“

JTAG Indirect ConfIguration File(.jic)

-

“

Configuration device:

”栏是

flash

的型号,选择“

EPCS16

”

-

File name:

”栏是选择输出

.jic

文件的位置,“

led\quartus_prj\output_files

”,并重命名为“led.jic

”

-

点击“Input files to convert”框中的“Flash Loader”后会发现“Add Device…”从不能被选择的情况下可以被选择,然后点击“Add Device…”,

选择使用的

FPGA

芯片所属的型号,在“

Device family

”框中将“Cyclone IV E

”前的括号勾选上,在“

Device name

”框中将“

EP4CE10

”前的括号勾选上,然后点击“OK

”

- 点击“Input files to convert”框中的“Sof Data”后会发现“Add File…”可以被选择,然后点击“Add File…”

- 因 为“ led.jic ”文件的生成需要“ led.sof ”文件的参与,所以选择路路径“led\quaruts_prj\output_files”下的“led.sof”文件后点击“Open”

-

然后点击“

Generate

”生成“

led.jic

”文件

下载至Flash中

-

回到下载界面,右击“

led.sof

”,点击“

Delete

”将其删除

-

点击“

Add File…

”将“

led.jic

”文件添加进来

-

将“

Program/Configure

”下的方框打上钩,然后点击“

Start

”执行程序的固化

注:

-

教材里提到为了避免一些安全隐患,需要对

未使用的管脚进行默认设置

。详见书165页。 -

勿热插拔

,先去电再拔下载器

版权声明:本文为weixin_42569890原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。