目录

3.2.1 Internal 1.2-V Switching Regulator(DC-DC)

3.3 Device Identification and Configuration Registers

3.4.6 NMI Watchdog Reset (NMIWDRS)

3.5.3 Interrupt Entry Sequence

3.5.4 Configuring and Using Interrupts

3.1 Introduction

系统级配置由一组子模块控制,这些子模块统称为系统控制模块。系统控制模块提供以下功能:

系统级重置,包括通电和断电重置

- 时钟源选择和PLL(锁相环)配置

- 时钟缺失检测

- 时钟选通低功率模式

- 外围中断处理

- 某些故障条件下的不可屏蔽中断

- 3个32位的定时器

- 窗口看门狗定时器,可产生中断或重置

- RAM初始化、写保护和主控

- 闪存ECC、等待状态和缓存配置

- 双区号安全模块

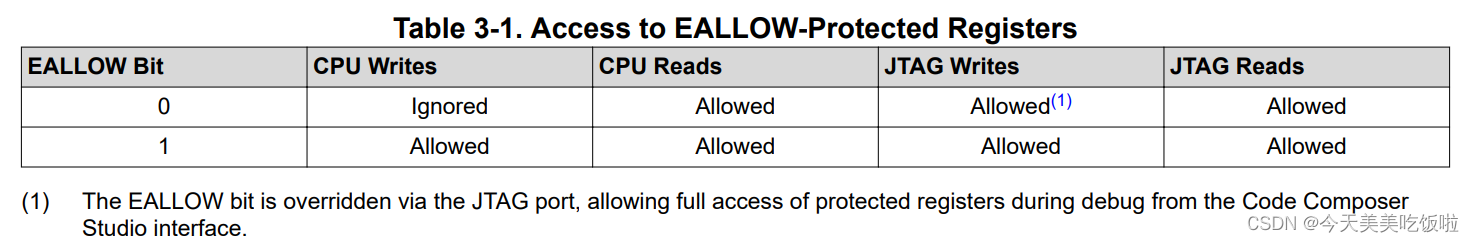

系统中的一些寄存器通过EALLOW保护机制受到保护,不受虚假CPU写入的影响。这使用特殊的CPU指令EALLOW和EDIS来启用和禁用对受保护寄存器的访问。当前保护状态由CPU的ST1寄存器中的EALLOW位给出。

启动时默认启用寄存器保护。受保护时,CPU对受保护寄存器的所有写入都被忽略。只允许CPU读取、JTAG读取和JTAG写入。如果通过执行EALLOW指令禁用保护,则允许CPU自由写入受保护的寄存器。在修改寄存器后,可以通过执行EDIS指令来清除EALLOW位来再次保护它们。

通过写入特殊锁寄存器,可以禁用对时钟配置和外围时钟启用寄存器的写入,直到下一次重置。

3.2 Power Management

3.2.1 Internal 1.2-V Switching Regulator(DC-DC)

默认情况下,内部DC-DC调节器禁用。要使用该电源,TMS320F28004x MCU核心必须首先使用内部LDO(VREG)通电,然后通过应用软件转换到内部DC-DC稳压器。请注意,内部LDO和内部DC-DC都需要VREGENZ low才能正常工作。执行以下程序以启用内部DC-DC调节器:

- EALLOW

- 设置DCCTL.DCDCEN位。

-

等待DCSTS.SWSEQDON等于0x1。

- 如果未设置该位,则从VREG到DC-DC的转换不成功(检查应用板上的硬件连接)。有关原理图的详细信息,请参阅TMS320F28004x实时微控制器数据手册。

-

检查DCSTS.INDDETECT等于0x1。

- 如果未设置该位,则VSW引脚上未检测到电感器。

- 如果检测到电感器,延迟80μs,以使DC-DC调节器输出稳定

- EDIS

启用内部DC-DC调节器的程序必须在所有其他初始化功能和应用代码之前完成。

应用程序可以随时切换回内部LDO。这可以通过清除DCCTL来实现。DCDCEN位并等待80μs,以使内部LDO通电。

注:

将DCDCEN设置为1会自动将GPIO22和GPIO23置于模拟模式;因此,不需要在开启DCDC时为GPIO22和GPIO23配置AMSEL。

3.3 Device Identification and Configuration Registers

设备标识寄存器和配置寄存器提供有关设备的零件号、产品系列、版本、管脚计数、合格状态和功能可用性的信息

所有设备信息都是DEV\u CFG\u REGS空间的一部分。标识寄存器为PARTIDL、PARTIDH和REVID

UID\u REGS中有一个256位的唯一ID(UID)。256位被分离到这些寄存器中

- UID\u PSRAND0-5:192位伪随机数据

- UID\u UNIQUE:32位唯一数据,此寄存器中的值在具有相同部分的所有设备上都是唯一的

- UID\u校验和:UID\u PSRAND0-5和UID\u UNIQUE的32位fletcher校验和,在工厂测试期间计算为小端或大端

3.4 Reset

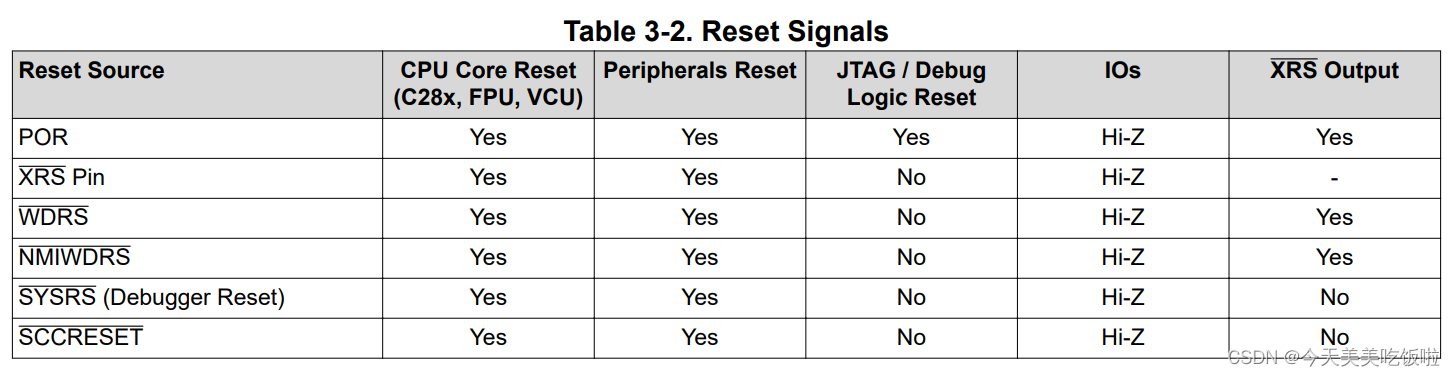

本节解释了该设备上不同复位的类型和效果。

3.4.1 Reset Sources

表3-2总结了各种复位信号及其对设备的影响。

重置可分为两组:

- 芯片级重置(XRS、POR、BOR、WDR和NMIWDR),重置所有或几乎所有设备。

- 系统重置(SYSR和SCCRESET),重置设备的大部分子集,但维持一些系统级配置。

重置后,重置原因寄存器(RESC)用重置原因更新。该寄存器中的位在多次重置中保持其状态。它们只能通过通电复位(POR)或将其写入RESCCLR寄存器来清除。一些被引导ROM清除,作为其启动例程的一部分

许多外围模块具有可通过SOFTPRESx寄存器访问的单独复位。有关模块复位状态的信息,请参阅该模块的相应章节。

在任何重置之后,CPU从启动ROM中的地址0x3FFFC0(重置向量)开始执行。

在运行引导ROM代码后,CPU通常会转移到地址0x80000处的闪存开始。有关控制引导过程的更多信息,请参阅ROM代码和外围设备引导一章。

注:

POR后,引导ROM将清除M0\/M1、LSx、GSx和消息RAM,以确保它们包含有效的ECC或奇偶校验。

3.4.2 External Reset (XRS)

外部复位(XRS)是设备的主芯片级复位。它重置CPU、所有外围设备和I/O引脚配置以及大多数系统控制寄存器。XRS有一个专用的开漏引脚。该引脚可用于驱动应用中其他集成电路的复位引脚,其本身也可由外部电源驱动。

XRS在看门狗、NMI和通电复位期间内部驱动。

无论何时XRS因任何原因被驱动为低电平,都将设置RESC寄存器中的XRSn位。该位随后由引导ROM清除。

3.4.3 Power-On Reset (POR )

通电复位(POR)电路在通电期间在整个设备中创建干净的复位,从而抑制GPIO上的故障。在POR期间,XRS引脚保持在低位。在大多数应用中,XRS保持较低的时间足以重置其他系统IC,但某些应用可能需要更长的脉冲。在这些情况下,XRS引脚可以从外部驱动到低电平,以提供正确的复位持续时间。POR重置XRS所做的一切,以及一些其他寄存器–重置原因寄存器(RESC)、NMI阴影标志寄存器(NMISHDFLG)和X1时钟计数器寄存器(X1CNT)。POR还重置JTAG端口使用的调试逻辑。

在POR之后,设置RESC中的POR和XRSn位。这些位随后被引导ROM清除。

3.4.4 Debugger Reset (SYSRS)

在开发过程中,有时需要在不断开调试器或中断系统级配置的情况下重置CPU及其外围设备。为了方便这一点,CPU有自己的子系统重置,可以使用Code Composer Studio由调试器触发™ 石斑鱼类。这种重置(SYSRS)重置CPU、其外围设备、许多系统控制寄存器(包括其时钟选通和LPM配置)以及所有I/O引脚配置。

SYSRS不会重置ICEPick调试模块、设备能力寄存器、时钟源和PLL配置、丢失的时钟检测状态、饼图矢量提取错误处理程序地址、NMI标志、模拟微调或仅由POR重置的任何内容(见第3.4.3节)。

3.4.5 Watchdog Reset (WDRS)

该设备有一个看门狗计时器,如果CPU在用户指定的时间内没有为其提供服务,则可以选择触发重置。该看门狗重置(WDRS)产生持续512个周期的XRS。

看门狗重置后,设置RESC中的WDRSn位。

3.4.6 NMI Watchdog Reset (NMIWDRS)

该设备有一个不可屏蔽中断(NMI)模块,用于检测系统中的硬件错误。NMI模块有一个看门狗计时器,如果CPU在用户指定的时间内没有响应错误,则会触发重置。此NMI看门狗重置(NMIWDRS)产生持续512个周期的XRS。

NMI看门狗重置后,设置RESC中的NMIWDRSn位。

3.4.7 DCSM安全代码复制重置(SCCRESET)

该设备具有双区码安全模块(DCSM),可阻止对闪存某些区域的读取访问。为了方便CRC检查和CLA代码的复制,TI提供了ROM功能来安全地访问这些内存区域。为了防止安全漏洞,在调用这些函数之前必须禁用中断。如果在安全复制或CRC函数中发生向量提取,DCSM会触发重置。此安全重置(SCCRESET)类似于SYSRS。然而,安全重置也会重置调试逻辑,以拒绝潜在攻击者的访问。

安全重置后,设置RESC中的SCCRESETn位。

3.5 Peripheral Interrupts

本节解释了设备上的外围中断处理。第3.6节介绍了不可屏蔽中断。本文档不包括软件中断和仿真中断。有关这些信息,请参阅《TMS320C28x CPU和指令集参考指南》。

3.5.1

Interrupt Concepts

中断是导致CPU暂停其当前执行并转移到另一段代码(称为中断服务例程(ISR))的信号。这是一种处理外围事件的有用机制,与寄存器轮询相比,它涉及更少的CPU开销或程序复杂性。然而,由于中断与程序流是异步的,因此必须注意避免在中断和主程序代码中访问的资源冲突.

中断通过一系列标志和启用寄存器传播到CPU。标志寄存器存储中断,直到对其进行处理。启用寄存器阻止中断的传播。当中断信号到达CPU时,CPU从称为向量表的列表中获取适当的ISR地址

3.5.2 Interrupt Architecture

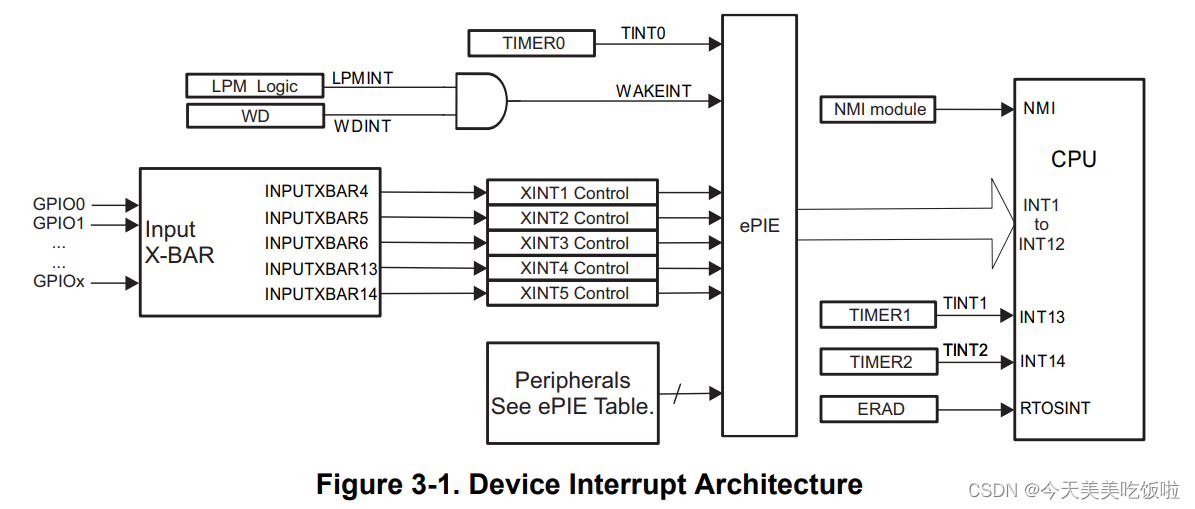

C28x CPU有十四条外围中断线。其中两个(INT13和INT14)分别直接连接到CPU计时器1和2。其余12个通过增强型外围中断扩展模块(ePIE,简称PIE)连接到外围中断信号。PIE将多达16个外围中断多路复用到每个CPU中断线。它还扩展了向量表,使每个中断都有自己的ISR。这允许CPU支持大量外围设备。

中断路径分为三个阶段——外围设备、饼图和CPU。每个阶段都有自己的启用和标志寄存器。该系统允许CPU在其他中断挂起时处理一个中断,实现软件中的嵌套中断并确定其优先级,并在某些关键任务期间禁用中断。

图3-1显示了该设备的中断架构。

3.5.2.1 Peripheral Stage

每个外设都有自己独特的中断配置,这在该外设的章节中进行了描述。一些外围设备允许多个事件触发同一中断信号。例如,通信外围设备可能使用相同的中断来指示已接收到数据或存在传输错误。

可以通过读取外设的状态寄存器来确定中断的原因。通常,在生成另一个中断之前,必须手动清除状态寄存器中的位。

3.5.2.2 PIE Stage

饼图为每个外围中断信号(有时称为饼图通道)提供单独的标志和启用寄存器位。这些通道根据其相关的CPU中断进行分组。每个饼图组有一个16位启用寄存器(PIEIERx)、一个16位标志寄存器(PIEIFRx)和一位饼图确认寄存器(PIEACK)。PIEACK寄存器位充当整个PIE组的公共中断掩码。

当CPU接收到中断时,它从PIE中获取ISR的地址。饼图返回组中编号最低的通道的向量,该通道已标记并启用。这使编号较低的中断在多个中断挂起时具有更高的优先级。

如果没有同时标记和启用中断,饼图将返回通道1的向量。除非软件在中断传播时更改饼图的状态,否则不会发生这种情况。第3.5.4节包含启用中断后安全修改PIE配置的程序。

3.5.2.3 CPU Stage

与饼图一样,CPU为其每个中断提供标志和启用寄存器位。有一个启用寄存器(IER)和一个标志寄存器(IFR),它们都是内部CPU寄存器。还有一个全局中断掩码,由ST1寄存器中的INTM位控制。可以使用CPU的SETC和CLRC指令设置和清除此掩码。在C代码中,C2000Ware的DINT和EINT宏可用于此目的。

对IER和INTM的写入是原子操作。特别是,如果设置了INTM,则管道中的下一条指令将在禁用中断的情况下运行。不需要软件延迟。

3.5.3 Interrupt Entry Sequence

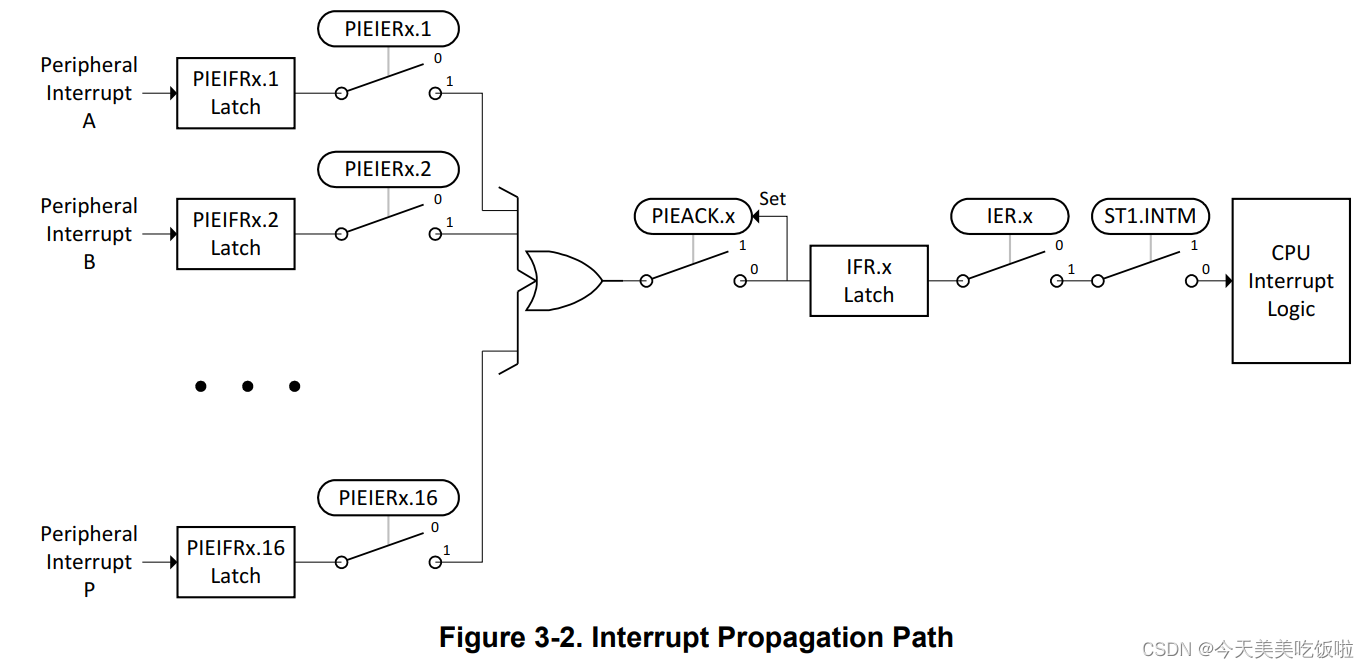

图3-2显示了外围中断如何传播到CPU。

当外围设备产生中断(在饼图组x、通道y上)时,它会触发以下事件序列:

- 中断锁存在PIEIFRx.y

- 如果PIEIERx.y置位时,中断传播。

- 如果PIEACK.x被清除,中断传播并且PIEACK.x被置位。

- 中断锁存在IFR.x。

- 如果IER.x置位,中断传播。

- 如果INTM清除,CPU接收中断。

- D2或管道后期中的任何指示都将运行到完成。刷新早期阶段的指令。

- CPU将其上下文保存在堆栈上。

- IFR.x和IER.x被清除。INTM被置位。EALLOW已清除。

- CPU从PIE中获取ISR向量。PIEIFRx.y被清除。

- CPU跳转到ISR。

中断延迟是PIEIFRx之间的时间。y锁存中断和进入CPU管道执行阶段的第一条ISR指令。最小中断延迟为14个SYSCLK周期。ISR或堆栈内存上的等待状态将增加延迟。外部中断为GPIO同步增加至少两个SYSCLK周期,再加上额外的输入确认时间(如果使用)。不能中断使用C28x RPT指令创建的循环。

3.5.4 Configuring and Using Interrupts

通电时,默认情况下不启用任何中断。PIEIER和IER寄存器被清除,INTM被设置。

应用程序代码负责配置和启用所有外围中断。

3.5.4.1 Enabling Interrupts

要启用外围中断,请执行以下步骤:

- 全局禁用中断(DINT或SETC INTM)。

- 通过设置PIECTRL寄存器的ENPIE位来启用PIE。

- 将每个中断的ISR向量写入PIE向量表中的适当位置,如表3-3所示。请注意,向量表受低保护。

- 为每个中断设置适当的PIEIERx位。PIE和通道分配见表3-3。

- 为包含已启用中断的任何饼图组设置CPU IER位。

- 在外围设备中启用中断。

- 全局启用中断(EINT或CLRC INTM)。

步骤4不适用于直接连接到CPU的定时器1和定时器2中断。

3.5.4.2 Handling Interrupts

ISR类似于正常功能,但必须做到以下几点:ISR类似于正常功能,但必须做到以下几点:

- 保存并恢复某些CPU寄存器(如果使用)的状态。

- 清除中断组的PIEACK位。

- 使用IRET指令返回。

如果使用中断关键字定义函数,则要求1和3由TMS320C28x C编译器自动处理。有关此关键字的信息,请参阅《TMS320C28x优化C\/C++编译器v6.2.4用户指南》的“关键字”部分。有关编写汇编代码以处理中断的信息,请参阅《TMS320C28x CPU和指令集参考指南》的“可屏蔽中断的标准操作”一节。

中断组的PIEACK位必须在用户代码中手动清除。这通常在ISR结束时完成。如果PIEACK位未被清除,CPU将不会收到来自该组的任何进一步中断。这不适用于定时器1和定时器2中断,它们不会通过PIE。

3.7 时钟

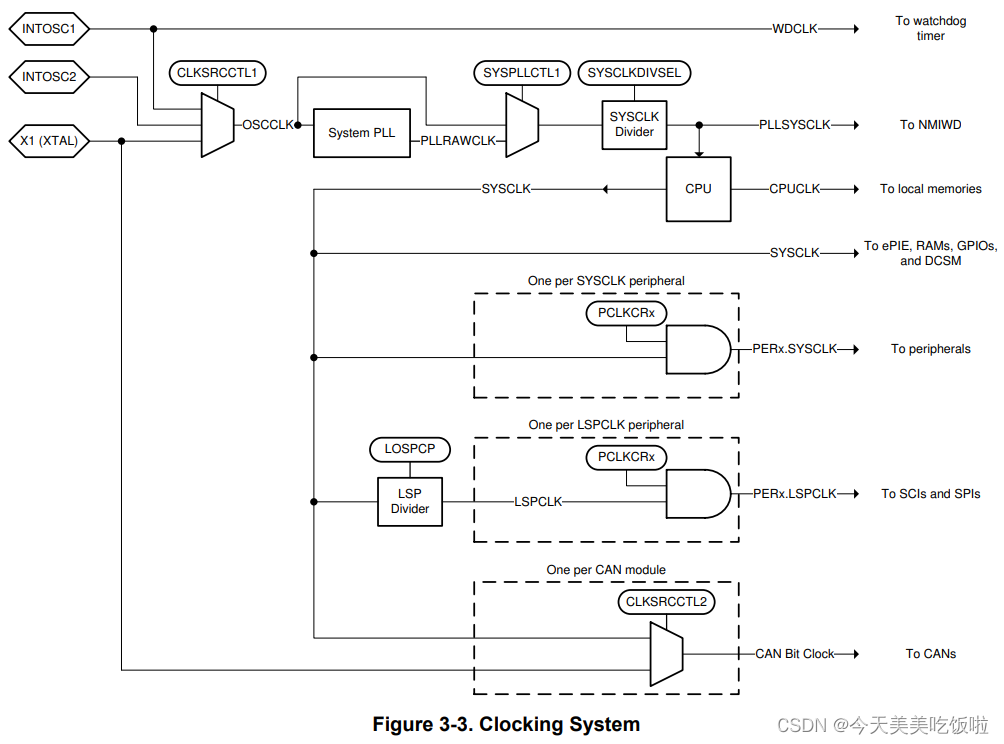

本节介绍此设备上的时钟源和时钟域,以及如何配置它们以供应用程序使用。图3-3和图3-4提供了设备时钟系统的概述。

3.7.1 时钟源

设备中的所有时钟都来自四个时钟源之一。

3.7.1.1 主内部振荡器 (INTOSC2)

通电时,设备由片上10MHz振荡器(INTOSC2)计时。INTOSC2是主要的内部时钟源,是复位时的默认系统时钟。INTOSC2用于运行引导ROM,并可用作应用程序的系统时钟源。请注意,INTOSC2频率公差太过宽松,无法满足CAN的定时要求。使用CAN模块需要外部振荡器。当INTOSC2用作系统时钟源时,GPIO18(X2)可用作GPIO。必须将1k下拉电阻器连接到X1。由于与振荡器电路的相互作用,GPIO18具有与其他GPIO不同的电特性。有关更多信息,请参阅设备数据手册。

3.7.1.2 备用内部振荡器(INTOSC1)

该设备还包括一个冗余的片上10MHz振荡器(INTOSC1)。INTOSC1是一个备份时钟源,通常只对看门狗定时器和丢失时钟检测电路(MCD)进行计时。如果MCD启用并且检测到丢失的系统时钟,则系统PLL被旁路,所有系统时钟自动连接到INTOSC1。出于调试目的,INTOSC1也可以手动选择为系统时钟源。

3.7.1.3 外部振荡器 XTAL

该设备支持外部时钟源(XTAL),可作为主系统和can位时钟源。频率限制和定时要求可在设备数据手册中找到。外部时钟源使用X1和X2\/GPIO18引脚。通电后,可按照第3.7.6节中的程序启用X1和X2引脚功能。

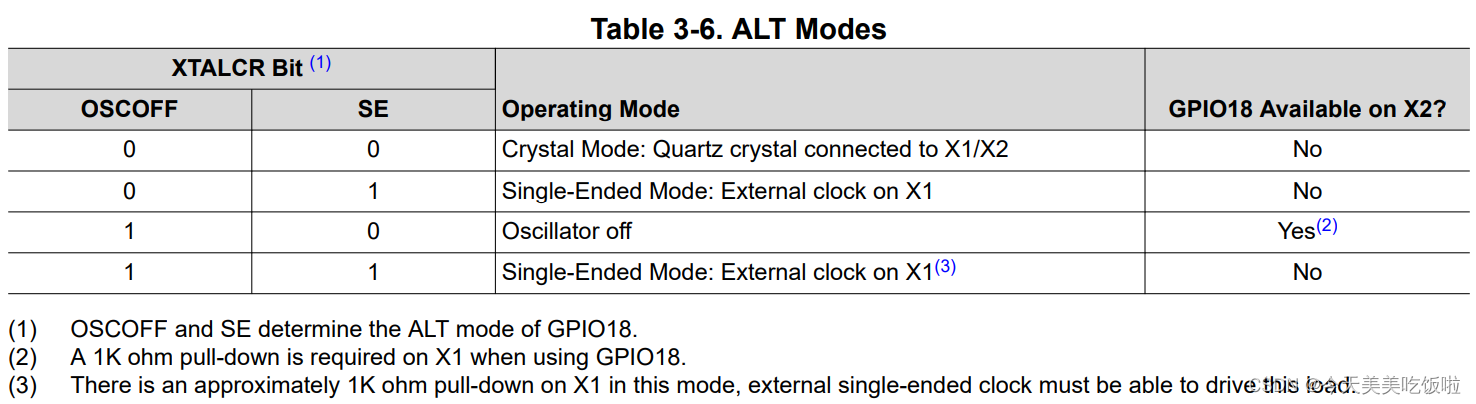

支持三种类型的外部时钟源:

-

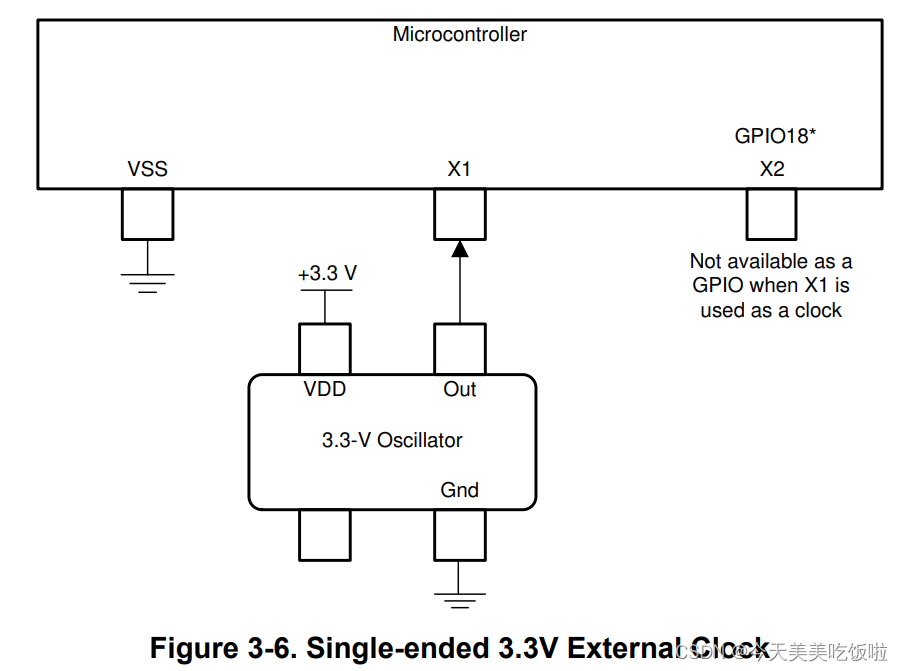

单端3.3V外部时钟。时钟信号连接到X1,如图3-6所示。X2\/GPIO18不能用作GPIO。

-

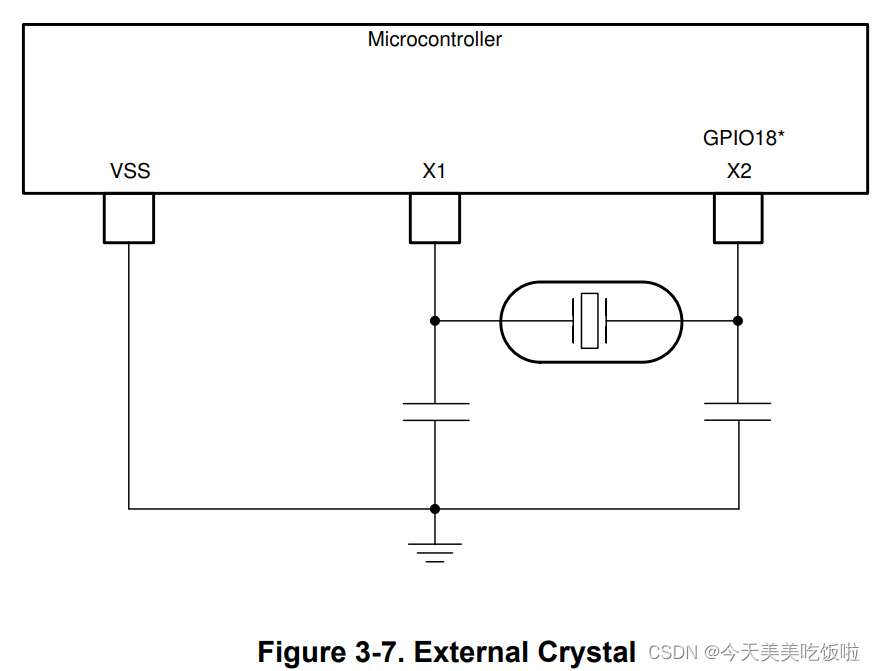

外部晶体。晶体跨X1和X2连接,负载电容器连接到VSS,如图3-7所示

-

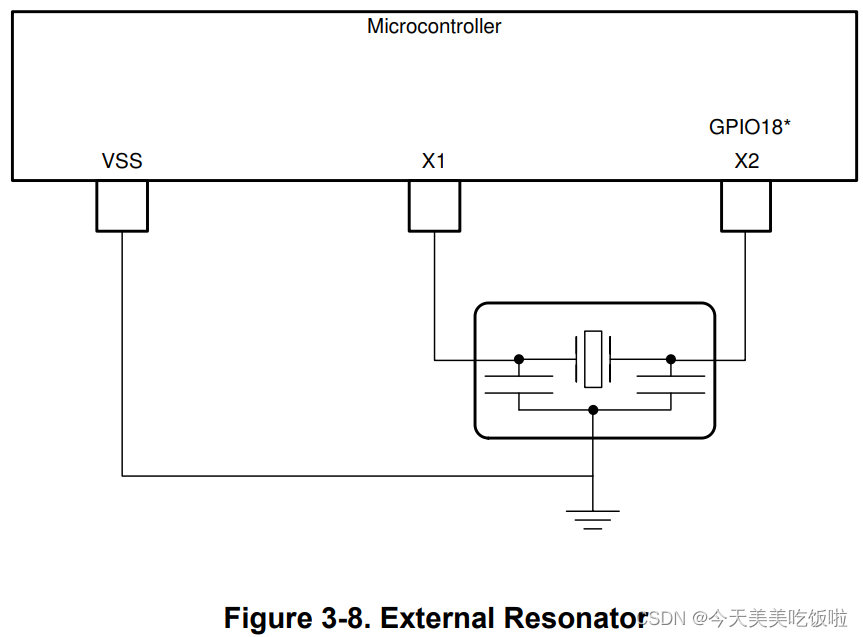

外部谐振器。谐振器跨X1和X2连接,接地连接至VSS,如图3-8所示。

3.7.2 衍生时钟

上一节中讨论的时钟源可以相乘(使用PLL)并分频,以产生应用所需的时钟频率。此过程生成一组派生时钟,本节将对此进行描述

3.7.2.1 振荡器时钟 OSCCLK

必须选择INTOSC2、XTAL或INTOSC1之一作为CPU和大多数外围设备的主参考时钟(OSCCLK)。OSCCLK可以直接使用或通过系统PLL馈送以达到更高的频率。复位时,

OSCCLK是默认系统时钟,并连接到INTOSC2

。

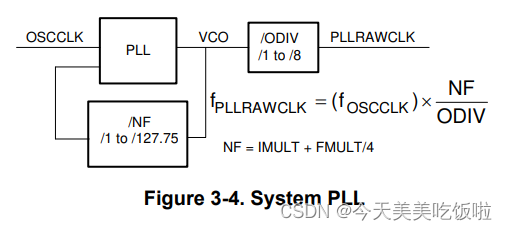

3.7.2.2 系统PLL输出时钟(PLLRAWCLK)

系统PLL允许设备以其最大额定工作频率运行,并且在大多数应用中将生成主系统时钟。该PLL使用OSCCLK作为参考,并具有分数乘法器。PLLRAWCLK是PLL的压控振荡器(VCO)的输出。有关配置说明,请参见第3.7.6节。

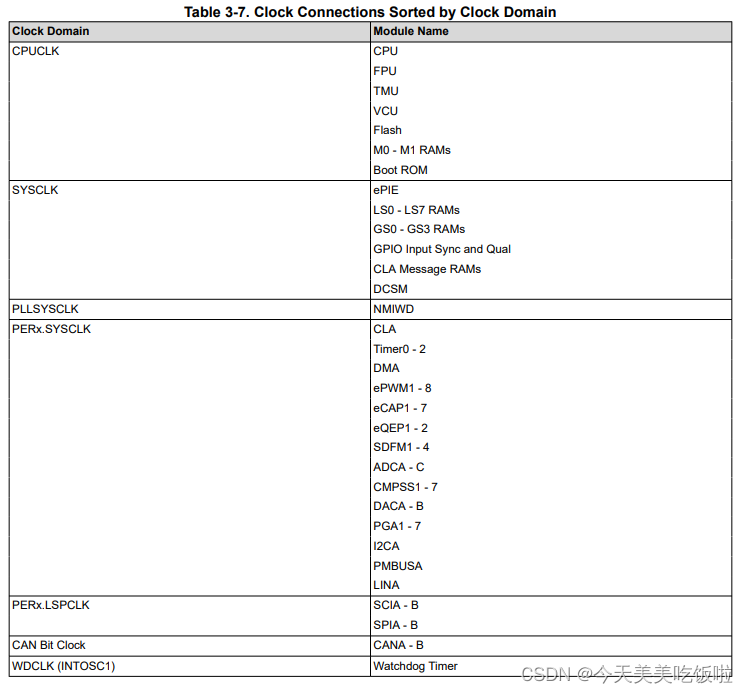

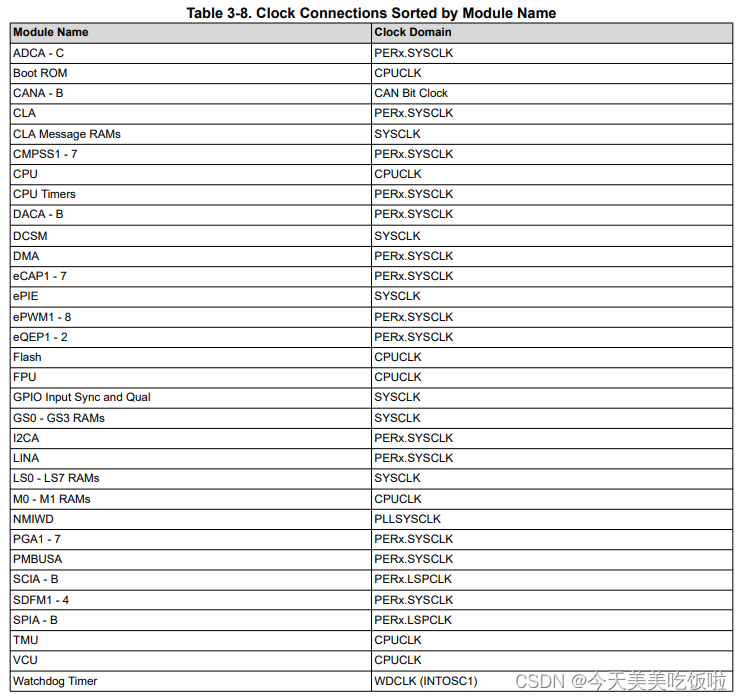

3.7.3设备时钟域

设备时钟域向设备中各个模块的时钟输入馈电。它们直接或通过附加分频器连接到派生时钟

3.7.3.1 系统时钟PLLSYSCLK

NMI看门狗定时器有自己的时钟域(PLLSYSCLK)。尽管名称不同,PLLYSCLK可以连接到系统PLL(PLLRAWCLK)或OSCCLK。所选时钟源通过分频器运行,该分频器使用SYSCLKDIVSEL寄存器进行配置。PLLSYSCLK在HALT模式下选通。

3.7.3.2 CPU时钟 CPUCLK

CPU有一个时钟(CPUCLK),用于为CPU、协处理器、专用RAM(M0和M1)以及引导ROM和闪存包装器计时。该时钟与PLLYSCLK相同,但在CPU进入IDLE或HALT模式时被选通。

3.7.3.3 CPU子系统时钟(SYSCLK和PERx.SYSCLK)

CPU向CLA、DMA和大多数外围设备提供时钟(SYSCL)。该时钟与PLLYSCLK相同,但在CPU进入HALT模式时被选通。

每个外围时钟都有自己的独立时钟门控,由PCLKCRx寄存器控制。

3.7.3.4低速外围时钟(LSPCLK和PERx.LSPCLK)

SCI和SPI模块可以以比CPU频率慢得多的比特率进行通信。这些模块连接到共享时钟分频器,该分频器生成从SYSCLK导出的低速外围时钟(LSPCLK)。LSPCLK默认使用\/4除法器,但可以使用LOSPP寄存器更改比率。每个SCI和SPI模块的时钟(PERx.LSPCLK)可以使用PCLKCRx寄存器独立门控。

3.7.3.5 CAN时钟

CAN位时钟所需的频率容差取决于位定时设置和网络配置,可能高达0.1%。由于主系统时钟(PERx.SYSCLK形式)不够精确,位时钟也可以使用CLKSRCCTL2寄存器连接到XTAL。每个CAN模块都有一个独立的选择。

为了保持正确的操作,CAN位时钟的频率必须小于或等于SYSCLK频率。

3.7.3.6 CPU定时器2时钟(TIMER2CLK)

CPU定时器0和1连接到PERx.SYSCLK。定时器2默认连接到PERx.SYSCLK,但也可以使用TMR2CLKCTL寄存器连接到INTOSC1、INTOSC2或XTAL。该寄存器还为定时器2提供单独的预分频器。如果使用非SYSCLK源,则必须将源分频至不超过SYSCLK频率的一半。

使用非SYSCLK源的主要原因可能是用于内部频率测量。在大多数应用程序中,计时器2会关闭SYSCLK。

3.7.4 XLCKOUT

为了调试和测试,有时需要直接观察时钟。外部时钟输出(XCLKOUT)功能通过将时钟连接到外部引脚(可以是GPIO16或GPIO18)来支持此功能。可用的时钟源有PLLSYSCLK、PLLRAWCLK、SYSCLK、INTOSC1、INTOSC2和XTAL。

要使用XCLKOUT,首先使用CLKSRCCTL3寄存器选择时钟源。接下来,使用XCLKOUTDIVSEL寄存器选择所需的输出除法器。最后,使用GPIO配置寄存器将GPIO16或GPIO18连接到多路复用器信道11。

3.7.5 时钟连接