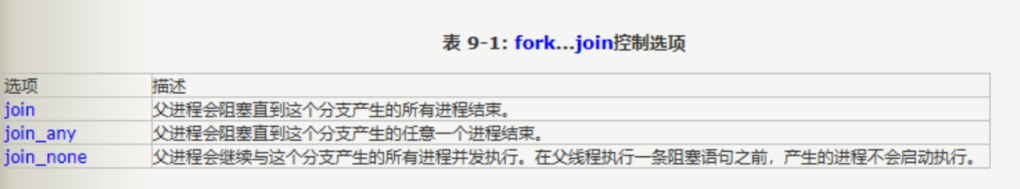

1、systemverilog 中以下语句哪一个表示等待至少一个进程完成,然后再执行后继语句?

A、fork…join…any

B、fork…join…none

C、fork…join…one

D、fork…join

知识拓展:

2、Linux常用命令中,下列哪个用于修改文件所属群组

A、chown

B、cat

C、chmod

D、chgrp

解析:

cat是concat enate的简写,cat命令用于连接文件或标准输入并打印;

chmod=change mode,改变读写模式

chown=change owner,修改文件所属用户

chgrp=change group

3、verilog HDL中信号没有定义数据类型时,缺省为什么数据类型?

A、z

B、wire

C、tri

D、reg

解析:

verilog程序模块中输入输出信号类型默认自动定义成wire型;

wire型,默认为高阻值z;

补充,systemverilog中,logic不能被多个结构驱动,多个驱动只能用wire。

4、超大规模集成电路设计中,为了高速设计,采取以下哪些措施

A、并行化设计

B、串行化设计

C、流水线设计

D、资源共享

解析:

[AC]高速设计要求并行化和流水线设计,牺牲集成电路面积,牺牲功耗。

5、在验证中下列关于代码覆盖率描述错误的是

A、代码覆盖率包括语句覆盖率

B、代码覆盖率包括条件覆盖率

C、代码要盖率包括功能覆盖率

D、代码要盖率达到100%说明所有Bug已消除

解析:

代码覆盖率包括行覆盖率(语句覆盖率)、路径覆盖率、翻转覆盖率、有限状态机FSM覆盖率。

6、数字电路的验证维度有哪些

A、完备性

B、满足性能

C、复用性

D、高效性

解析:

[ABCD]

ic验证能力的五个维度:

完备性、代码性能、复用性、高效性、高产出.

7、下列哪些方式可以减少亚稳态问题的影响

A、提升系统时种频率

B、改善时钟质量

C、用反应更快的FF

D、架构上降低data toggle rate

解析:

[BCD]

改善亚稳态的方法

1.降低系统时钟

2.用反应更快的FF

2.引入同步机制,防止亚稳态传播

3.改善时钟质量,用边沿变化快速的时钟信号

关键是器件使用比较好的工艺和时钟周期的裕量要大。

8、AMBA总线协议包含AXI。AHB______ ASB. (请全部用大写字母拼写回答)

解析:

AMBA规范主要包括以下三种:

- AHB(advanced high performance Bus即AMB高性能总线):用于高性能、高速局吞吐率部件,如CPU、DMA、DSP之间的连接;

- ASB(Advanced System Bus 即AMBA系统总线):用来作处理器与外设之间的互连,将被AHB取代。

- APB(Advanced Peripheral Bus,AMBA外设总线):为系统的低速外设提供低功耗的简易互联。

9、大端模式是指数据的高字节存放在_地址,低字节存放在_地址(填写:高”或者”低)

解析:

我们常用的X86结构是小端模式,而KEIL C51则为大端模式。很多的ARM, DSP都为小端模式。有些ARM处理器还可以由硬件来选择是大端模式还是小端模式。

采用大小模式对数据进行存放的主要区别在于在存放的字节顺序,

大端方式将高位存放在低地址,小端方式将高位存放在高地址

。采用大端方式进行数据存放符合人类的正常思维,而采用小端方式进行数据存放利于计算机处理。到目前为止,采用大端或者小端进行数据存放,其孰优孰劣也没有定论。

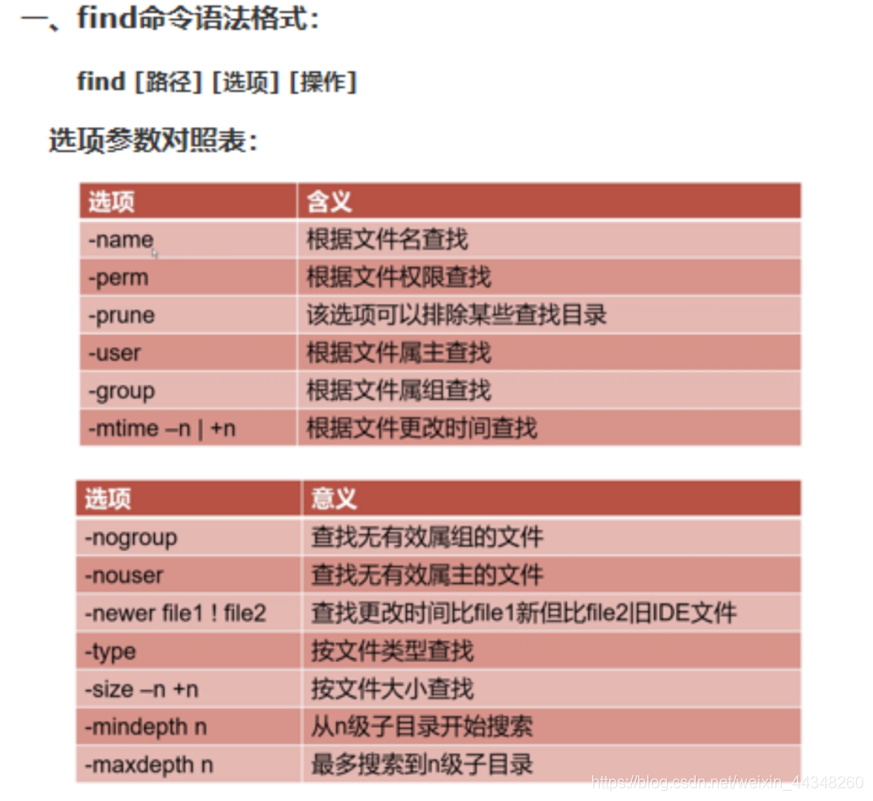

10、在L inux系统中,根据文件名查找文件位置的命令是

find -name xxx

解析:

11、在一个CPU系统中。如果有两个模块UART和TIMER可以向CPU发送中断(电平),由CPU进行控制中断清除,如何完备的验证中断?

1.构建验证环境env:包括channel. generater. driver. mopnitor和scoreboard .通过SV的随机配置函数产生中断信号,由driver驱动.再由channel传

入CPU中.通过monitor监测信号.再由scoreboard,

2.功能点测试功能点:①UART或者TIMER中断单-触发。CPU不清除。QUART或者TIMER同时中断触发 , CPU不清除。⑧UART或者TIMER未被触发 。

CPU进行清除中断处理。

3.搜集爱盖率:搜集功能要盖率,代码要盖率.尽量添加更多的测试用例.提升其要盖率。

12、请列出SRAM与DSRAM的不同之处?

RAM 随机存储器

:存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关的存储器。这种存储器在

断电时将丢失其存储

内容,故主要用于存储短时间使用的程序。

SRAM 表示静态态随机存取存储器

:因此只要供电它就会保持一个值。一般而言,SRAM 比DRAM 要快,这是因为 SRAM 没有刷新周期。每个 SRAM 存储单元由 6 个晶体管组成,而DRAM 存储单元由一个晶体管和一个电容器组成。成本更高

DRAM 表示动态随机存取存储器

:这是一种以电荷形式进行存储的半导体存储器。DRAM中的每个存储单元由一个晶体管和一个电容器组成。数据存储在电容器中。电容器会由于漏电而导致电荷丢失,因而 DRAM 器件是不稳定的。为了将数据保存在存储器中,DRAM 器件必须有规律地进行刷新。

SDRAM 同步动态随机存储器

:意思是指理论上其速度可达到与 CPU 同步。

DDR SDRAM(Dual Date Rate SDRAM):简称 DDR

,也就是“双倍速率 SDRAM“的意思。DDR 可以说是 SDRAM 的升级版本,DDR 在时钟信号上升沿与下降沿各传输一次数据,这使得 DDR 的数据传输速度为传统 SDRAM 的两倍。

ROM 指的是“只读存储器”

,即 Read-Only Memory。这是一种线路最简单半导体电路,通过掩模工艺, 一次性制造,其中的代码与数据将永久保存(除非坏掉),不能进行修改。

==PROM 指的是“可编程只读存储器”==既 Programmable Red-Only Memory。这样的产品只允许写入一次,所以也被称为“一次可编程只读存储器”(One Time Progarmming ROM,OTP-ROM)。PROM 在出厂时,存储的内容全为 1,用户可以根据需要将其中的某些单元写入数据 0(部分的 PROM 在出厂时数据全为 0,则用户可以将其中的部分单元写入,以实现对其“编程”的目的。

EPROM指的是“可擦写可编程只读存储器”

,即Erasable Programmable Read-Only Memory。它的特点是具有可擦除功能,擦除后即可进行再编程,但是缺点是擦除需要使用紫外线照射一定的时间。

EEPROM 指的是“电可擦除可编程只读存储器”

,即 Electrically Erasable Programmable Read-Only Memory。它的最大优点是可直接用电信号擦除,也可用电信号写入。EEPROM 不能取代 RAM 的原因是其工艺复杂,耗费的门电路过多,且重编程时间比较长,同时其有效重编程次数也比较低。

Flash memory 指的是“闪存”

,所谓“闪存”,它也是一种非易失性的内存,属于 EEPROM 的改进产品。它的最大特点是必须按块(Block)擦除(每个区块的大小不定,不同厂家的产品有不同的规格), 而 EEPROM 则可以一次只擦除一个字节(Byte)。

13、请列出一般系统中的Memory hierarchy,并解释系统中为何需要将存储器分层?

现代计算机系统的存储系统是分层的,主要有六个层次:

(1)CPU寄存器

(2)On-chip L1 Cache (一般由static RAM组成,size较小,例如16KB)

(3)Off-chip L2 Cache (一般由static RAM组成,size相对大些,例如2MB)

(4)Main memory(一般是由Dynamic RAM组成,几百MB到几个GB)

(5)本地磁盘(磁介质,几百GB到若干TB)

(6)Remote disk(网络存储、分布式文件系统)

而决定这个分层结构的因素主要是:容量(capacity),价格(cost)和访问速度(access time)。位于金字塔顶端的CPU寄存器访问速度最快(一个clock就可以完成访问)、容量最小。金字塔底部的存储介质访问速度最慢,但是容量可以非常的大。