1. 掌握存储器的组成结构和工作原理。

2. 掌握静态随机存储器RAM工作特性及数据的读写方法。

PC

机一台,TD-CMA实验系统一套,USB线一根,排线若干。

三、实验原理

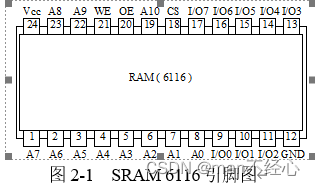

实验所用的静态存储器由一片6116(2K×8bit)构成(位于MEM单元),如图2-1所示。6116有三个控制线:CS(片选线)、OE(读线)、WE(写线),其功能如表2-1所示,当片选有效(CS=0)时,OE=0时进行读操作,WE=0时进行写操作,本实验将CS常接地。

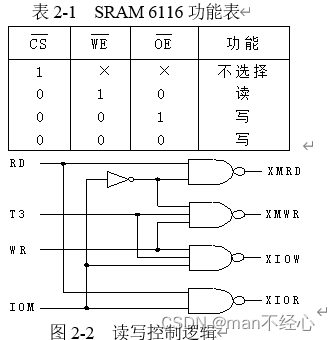

由于存储器(MEM)最终是要挂接到CPU上,所以其还需要一个读写控制逻辑,使得CPU能控制MEM的读写,实验中的读写控制逻辑如图2-2所示,由于T3的参与,可以保证MEM的写脉宽与T3一致,T3由时序单元的TS3给出(时序单元的介绍见附录2)。IOM用来选择是对I/O还是对MEM进行读写操作,RD=1时为读,WR=1时为写。

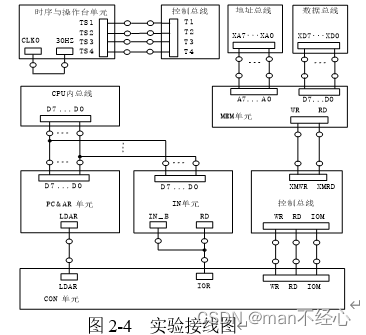

实验原理图如图2-3所示,存储器数据线接至数据总线,数据总线上接有8个LED灯显示D7…D0的内容。地址线接至地址总线,地址总线上接有8个LED灯显示A7…A0的内容,地址由地址锁存器(74LS273,位于PC&AR单元)给出。数据开关(位于IN单元)经一个三态门(74LS245)连至数据总线,分时给出地址和数据。地址寄存器为8位,接入6116的地址A7…A0,6116的高三位地址A10…A8接地。

实验箱中所有单元的时序都连接至时序与操作台单元,CLR都连接至CON单元的CLR按钮。实验时T3由时序单元给出,其余信号由CON单元的二进制开关模拟给出,其中IOM应为低(即MEM操作),RD、WR高有效,MR和MW低有效,LDAR高有效。

1.关闭实验系统电源,按图2-4连接实验电路,并检查无误,图中将用户需要连接的信号用圆圈标明。

2.将时序与操作台单元的开关KK1、KK3置为运行档、开关KK2置为‘单步’档(时序单元的介绍见附录二)。

3.将CON单元的IOR开关置为1(使IN单元无输出),打开电源开关,如果听到有‘嘀’报警声,说明有总线竞争现象,应立即关闭电源,重新检查接线,直到错误排除。

4.用一根USB线连接PC机和实验箱。

五、实验内容与实验步骤

1.给存储器的地址单元写入数据

写存储器的流程如图2-5所示(以向00地址单元写入11H为例):

2.读出储器的地址单元中的内容

读存储器的流程如图2-6所示(以从00地址单元读出11H为例):

3.存储器的读写操作

给存储器的01H、02H、03H、04H、05H地址单元中分别写入数据11H、22H、33H、44H、55H。依次读出第01H、02H、03H、04H、05H单元中的内容,观察上述各单元中的内容是否与前面写入的一致。

4.实现存储器两个单元的数据通过运算器进行指定的运算,并将运算结果写入存储器的操作。如:(01H)+(02H)=》06H

3.写操作:

- 执行完实验连接以及步骤以后,关掉存储器读写(WR=0,RD=0),数据开关地址(IOR=0),打开地址寄存器门控信号(LDR=1),按动ST产生T3脉冲,将地址打入AR中

- 关掉存储器读写(WR=0,RD=0)和地址寄存器门控信号(LDR=0),数据开关输出写入数据,打开输入三态门(IOR=0),使存储器处于写状态(WR=1,RD=0,IOM=0),按动ST产生T3脉冲,将数据打入存储器

读操作:

- 关闭存储器读写(WR=0,RD=0),按动ST产生T3脉冲,将地址打入AR

- 关闭IN单元输出(IOR=1),使存储器处于读状态(WR=0,RD=1,IOM=0),此时数据总线上的数即为从存储器当前地址中的数据内容。

具体步骤:

- 将IN单元 01H=0000 0001打入地址寄存器AR

- 将数据 11H=0001 0001 打入存储器MEM中

- 关闭IN单元的输出,读出MEM中的数据

- 将IN单元02H=0000 0010 打入地址寄存器AR

- 将数据 22H=0010 0010 打入存储器MEM中

- 关闭IN单元的输出,读出MEM中的数据

- 将IN单元 03H=0000 0011打入地址寄存器AR

- 将数据 33H=0011 0011 打入存储器MEM中

- 关闭IN单元的输出,读出MEM中的数据

- 将IN单元 04H=0000 0100打入地址寄存器AR

- 将数据 44H=0100 0100 打入存储器MEM中

- 关闭IN单元的输出,读出MEM中的数据

- 将IN单元 05H=0000 0101打入地址寄存器AR

- 将数据 55H=0101 0101 打入存储器MEM中

- 关闭IN单元的输出,读出MEM中的数据

5.通过软件中的数据通路图来观测实验结果

如果实验箱和PC联机操作,则可通过软件中的数据通路图来观测实验结果(软件使用说明请看附录1),方法是:打开软件,选择联机软件的“【实验】—【存储器实验】”,打开存储器实验的数据通路图,如图2-7所示。

六、思考题

1

.存储器实验电路图

2-7

能否实现存储器的

00

和

04

地址两个单元的内容交换?

在存储器实验当中,想要进行两个存储单元的交换,可以利用命令的方式来进行实现。如图2-7能够实现

存储器的

00

和

04

地址两个单元的内容交换。

2

.该存储器由一片静态存储器

SRAM6116(2Kx8)

组成,根据存储器实验原理图

2-3

,判断实际

可操作(或访问)的存储器的容量有多少?

根据存储器实验原理图

2-3

,

存储器数据线接至数据总线,数据总线上接有 8 个 LED 灯显 示 D7…D0 的内容。地址线接至地址总线,地址总线上接有 8 个 LED 灯显示 A7…A0 的内容, 地址由地址锁存器(74LS273,位于 PC&AR 单元)给出。数据开关(位于 IN 单元)经一个三 态门(74LS245)连至数据总线,分时给出地址和数据。地址寄存器为 8 位,接入 6116 的地址 A7…A0,6116 的高三位地址 A10…A8 接地,所以其实际容量为 256 字节。

3

.如何实现存储器容量的扩展?如何将存储器实验原理图

2-3

中存储器的容量扩展到

2Kx8

?

字扩展(增加存储字的数量)。如图2-3,存储器数据线接至数据总线,数据总线上接有 8 个 LED 灯显 示 D7…D0 的内容。地址线接至地址总线,地址总线上接有 8 个 LED 灯显示 A7…A0 的内容, 地址由地址锁存器(74LS273,位于 PC&AR 单元)给出。数据开关(位于 IN 单元)经一个三 态门(74LS245)连至数据总线,分时给出地址和数据。地址寄存器为 8 位。

字数不变,位数变长,因此选择字扩展。

需要的芯片数量=设计要求的存储容量/芯片的存储容量=(2K*8)/(0.25K*8)=8片

地址线:8=2^3 ,0.25K=2^8,因此需要地址线(3+8=11)

数据线:8根

七、实验分析和心得体会

通过这次实验让我了解了随机存储器是如何存储和读出数据的, 掌握了静态存储器的工作特性及数据读写方法,对数据通路及控制信号有了一定的了解。实验过程中,出现了送数据出错的问题,经过与其他同学的接线对比发现是接线问题。还有按动ST产生T3脉冲时,由于不确定什么步骤按动,导致数据通路图出现错误。通过查阅实验指导书知道T3脉冲按键时间,最终修正了数据通路图。实验过程中,我们应该要注意时序与操作台单元的开关KK1,KK3,KK2 是处于哪个档位,如本次实验,KK1,KK3为运行档,KK2为单步档。

另外我查阅网上资料也知道了,SRAM 是 RAM 的一种类型,其特性是数据在电源供电时可以静态地保存。每个 SRAM 单元由四个至六个晶体管组成,这些晶体管形成了一个双稳态触发器,它能够保存一位数据(0 或 1)。

SRAM 的读取和写入操作都是通过地址线进行的。读取操作时,首先通过地址线选择要读取的存储单元,然后通过数据线读取该存储单元中的数据。写入操作时,也是首先通过地址线选择要写入的存储单元,然后通过数据线将数据写入该存储单元。