详解建立时间和保持时间

1.定义:

建立时间和保持时间是数字电路-触发器(flip-flop)的一个概念。

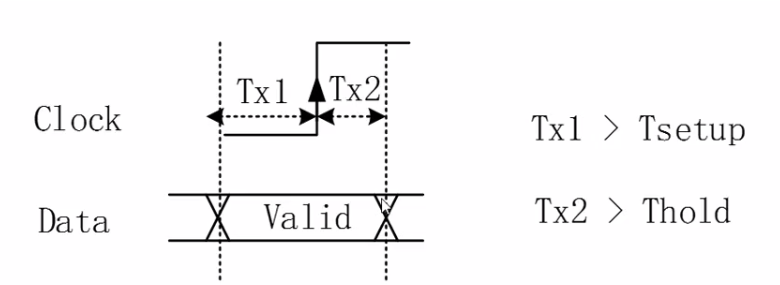

建立时间:在采样时钟沿到来之前,数据保持稳定的最小时间。

保持时间:在采样时钟沿到来之后,第二次数据到来之前,数据保持稳定的最小时间。

为什么要满足建立时间和保持时间?

因为触发器内部数据的形成是需要一定时间的。

如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值

2.特点:

3.建立时间分析

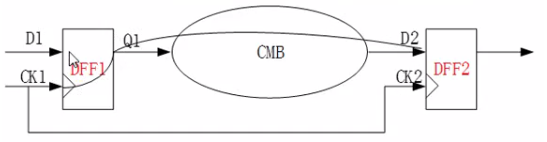

D触发器输入和输出会有内部延迟,用

T

c

k

Tck

T

c

k

表示,两个触发器之间有一段组合逻辑产生另外一个延迟,用

T

c

m

b

Tcmb

T

c

mb

表示,时钟偏斜,用

T

s

k

e

w

Tskew

T

s

k

e

w

表示。

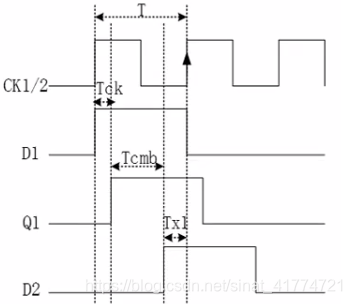

从图中可以看出,经过

T

c

k

Tck

T

c

k

数据到达

Q

1

Q1

Q

1

,经过

T

c

m

b

Tcmb

T

c

mb

,则

T

x

1

Tx1

T

x

1

可以用下式进行表示。

T

x

1

=

T

−

T

c

k

−

T

c

m

b

>

T

s

e

t

u

p

Tx1=T-Tck-Tcmb>Tsetup

T

x

1

=

T

−

T

c

k

−

T

c

mb

>

T

se

t

u

p

即

T

s

e

t

u

p

<

T

−

T

c

k

−

T

c

m

b

Tsetup<T-Tck-Tcmb

T

se

t

u

p

<

T

−

T

c

k

−

T

c

mb

考虑到

T

s

k

e

w

Tskew

T

s

k

e

w

晚到,则表达式可以改写为

T

s

e

t

u

p

<

T

+

T

s

k

e

w

−

T

c

k

−

T

c

m

b

Tsetup<T+Tskew-Tck-Tcmb

T

se

t

u

p

<

T

+

T

s

k

e

w

−

T

c

k

−

T

c

mb

所以对于建立时间违例,我们可以采取的措施有:

-

增大

TT

T

:增大时钟周期,即降低时钟频率 -

增大

Ts

k

e

w

Tskew

T

s

k

e

w

:在时钟路径上加缓冲器(buffer),让时钟更晚到来 -

减小

Tc

k

Tck

T

c

k

:更换具有更小器件延时的触发器 -

减小

Tc

m

b

Tcmb

T

c

mb

:组合逻辑优化,将串行的组合逻辑优化为并行逻辑,或在其中插入触发器

4.保持时间分析

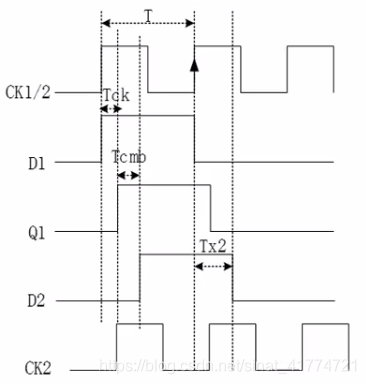

从图中可以看出

T

x

2

Tx2

T

x

2

的表达式如下:

T

x

2

=

T

c

k

+

T

c

m

b

>

T

h

o

l

d

Tx2=Tck+Tcmb>Thold

T

x

2

=

T

c

k

+

T

c

mb

>

T

h

o

l

d

考虑到

T

s

k

e

w

Tskew

T

s

k

e

w

晚到,则表达式可以改写为

T

x

2

=

T

c

k

+

T

c

m

b

−

T

s

k

e

w

>

T

h

o

l

d

Tx2=Tck+Tcmb-Tskew>Thold

T

x

2

=

T

c

k

+

T

c

mb

−

T

s

k

e

w

>

T

h

o

l

d

即

T

h

o

l

d

<

T

c

k

+

T

c

m

b

−

T

s

k

e

w

Thold<Tck+Tcmb-Tskew

T

h

o

l

d

<

T

c

k

+

T

c

mb

−

T

s

k

e

w

所以对于保持时间违例,我们可以采取的措施有:

-

增大

Tc

k

Tck

T

c

k

:更换具有更大器件延时的触发器 -

增大

Tc

m

b

Tcmb

T

c

mb

:增加组合逻辑运算时间 -

减小

Ts

k

e

w

Tskew

T

s

k

e

w

:优化时钟路径,让时钟更早到来

参考:https://blog.csdn.net/TechDiary/article/details/107410739