目录

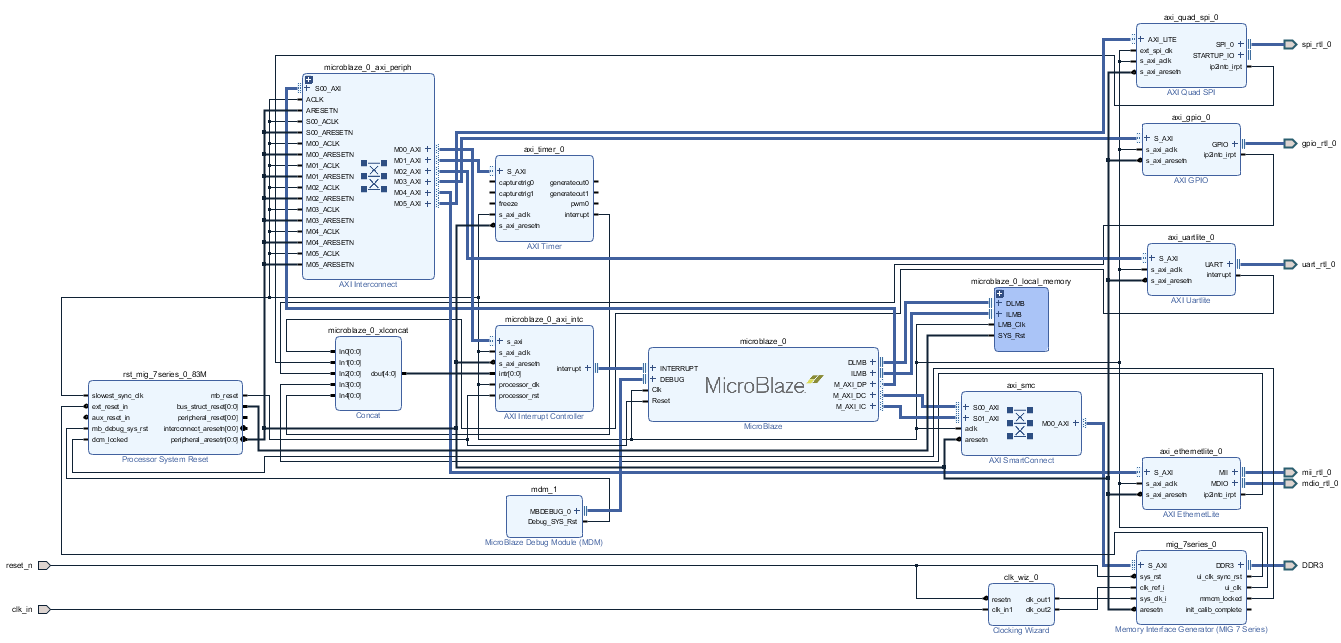

运行Linux需要UART串口通信模块,Timer定时器模块,ETH网络通信模块,还添加了GPIO模块用来指示程序运行状态,同时程序需要从SPI中加载,所以需添加DSPI模块。

下载工程

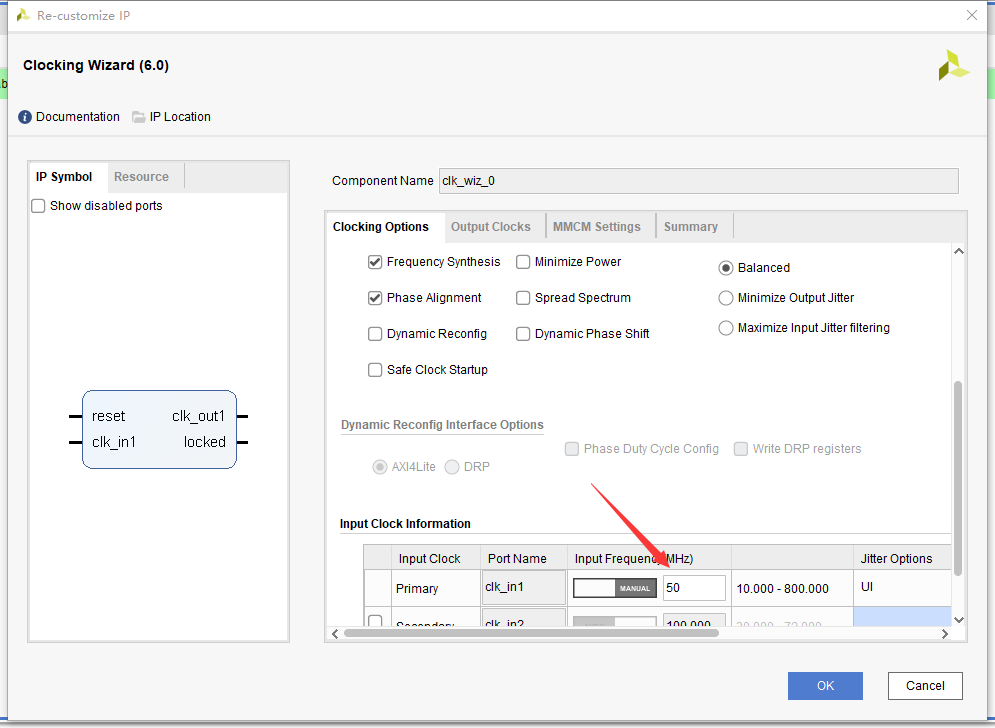

1.添加时钟模块

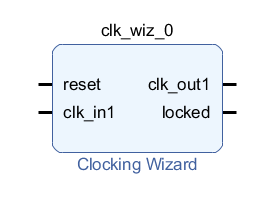

- 1.添加Clocking Wizard模块。

- 2.配置输入时钟频率为50MHz。

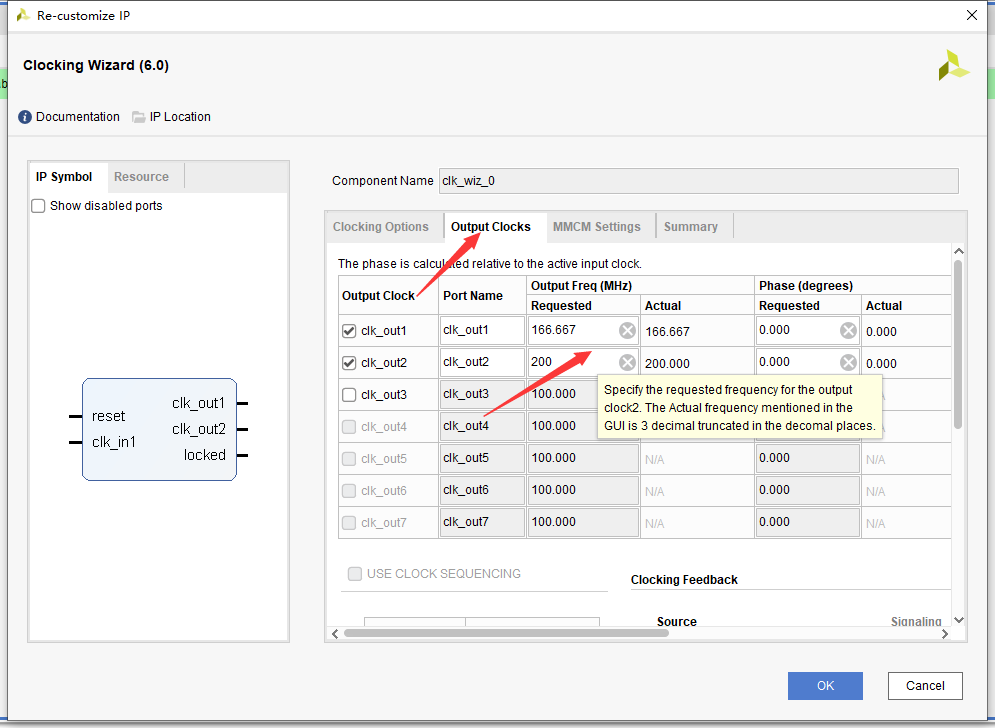

- 3.配置输出时钟频率。166.667MHz为DDR时钟,200MHz为Mig7模块参考时钟。

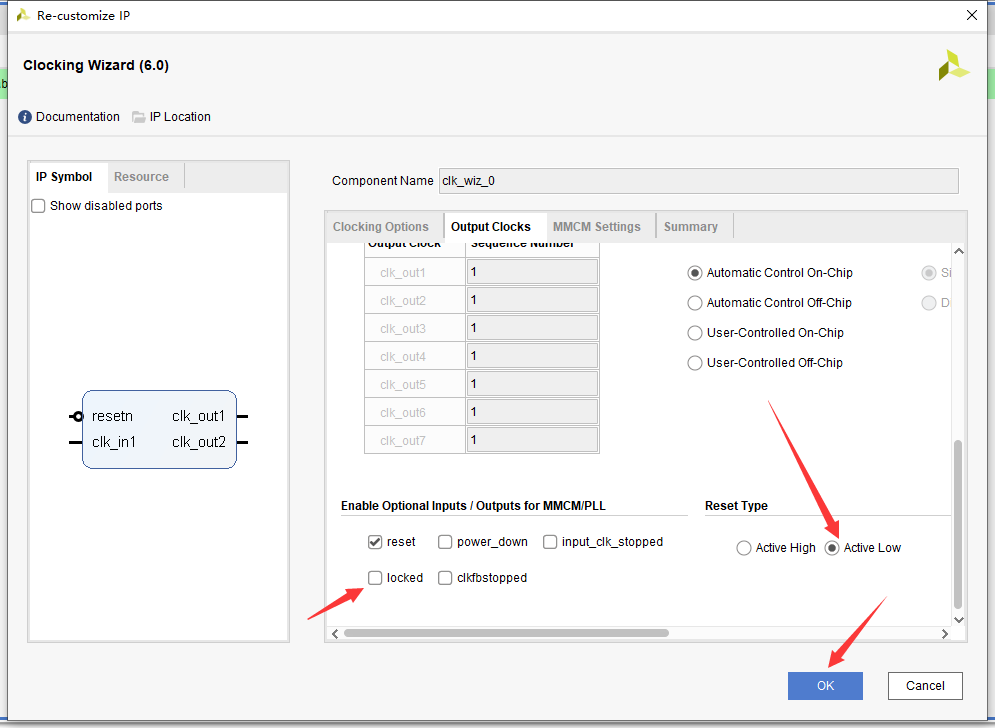

- 4.设置复位信号低电平有效,取消locked信号,单击OK完成设置。

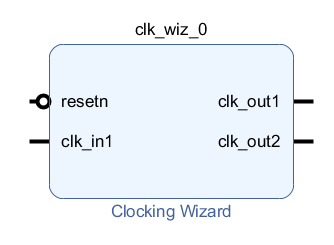

- 5.设置完成后如下图所示。

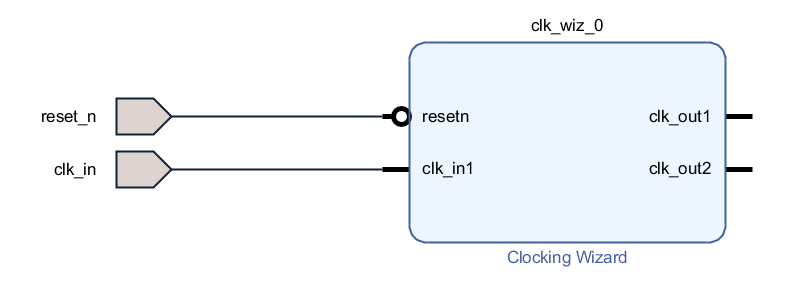

- 6.创建复位与时钟输入引脚。

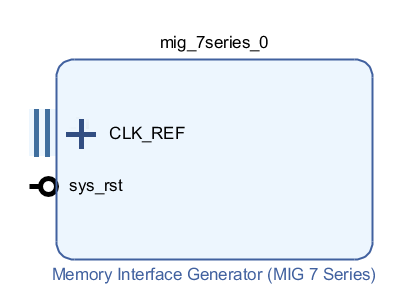

2.添加Mig7 DDR控制器模块

- 1.添加MIG 7 Series IP核。

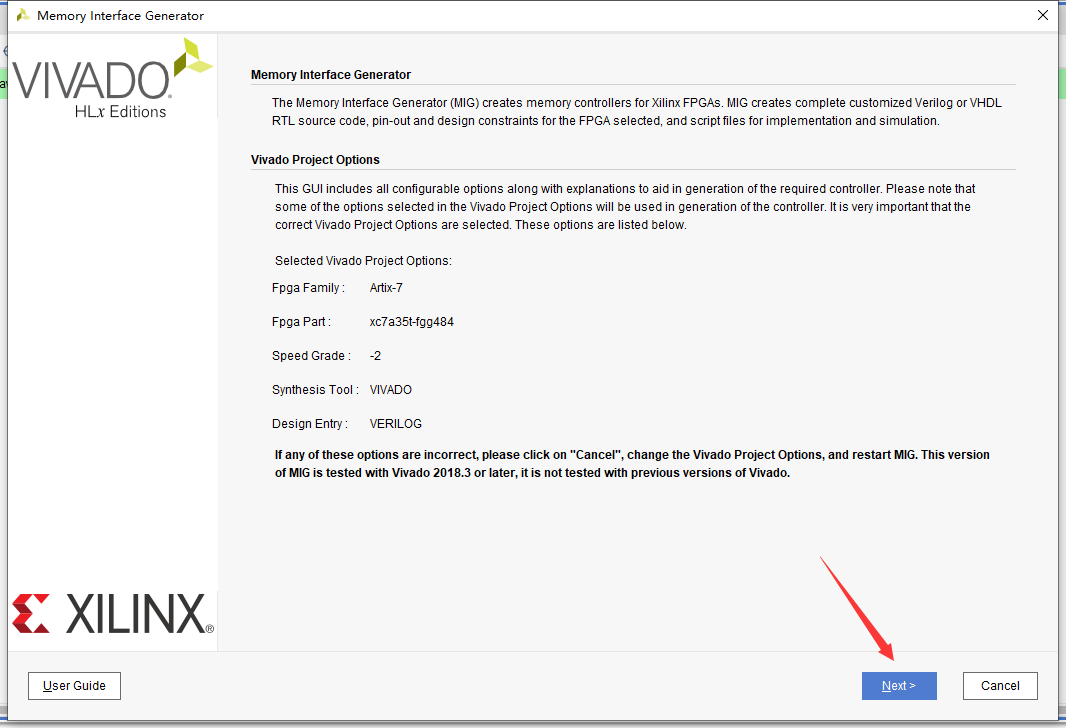

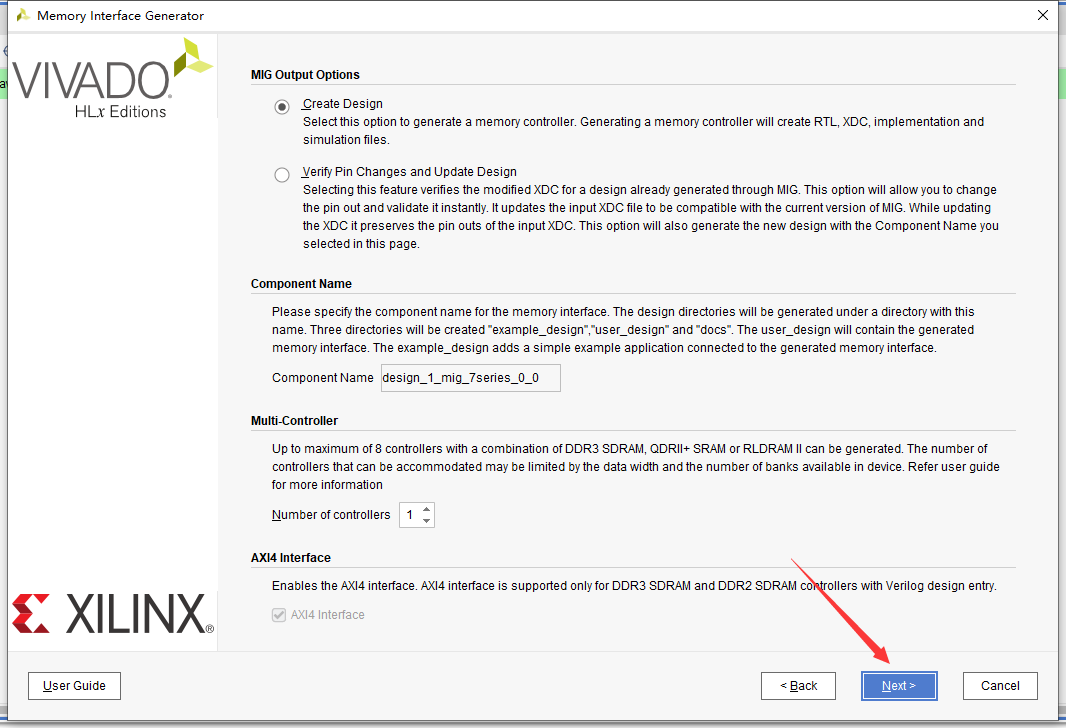

- 2.打开MIG设置界面

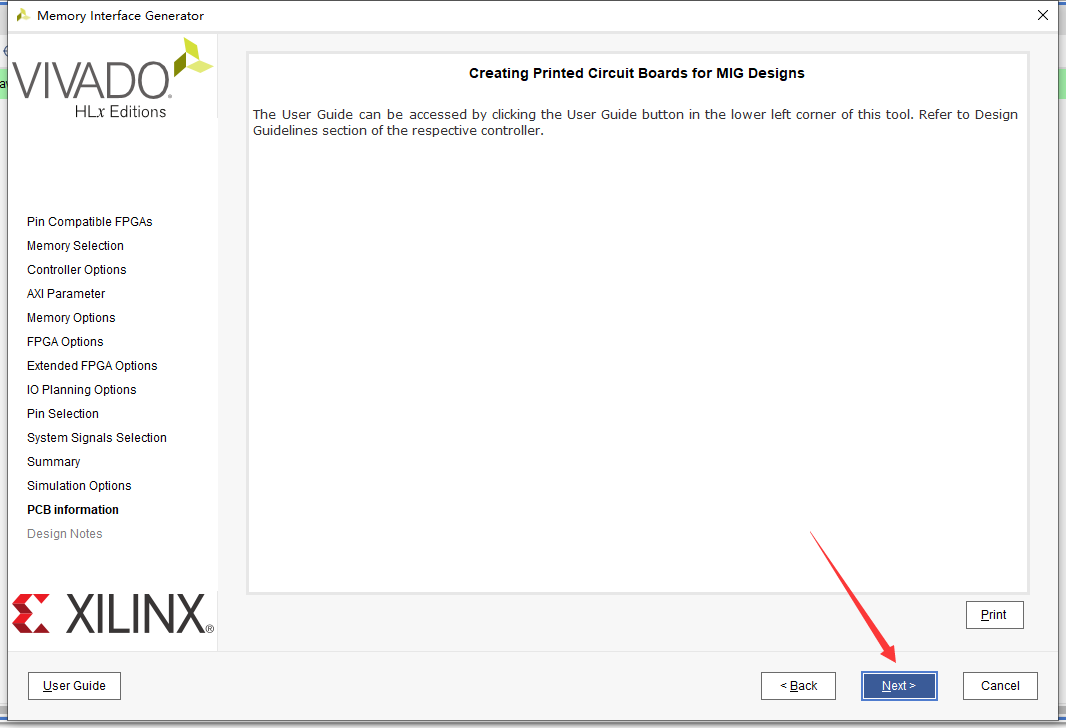

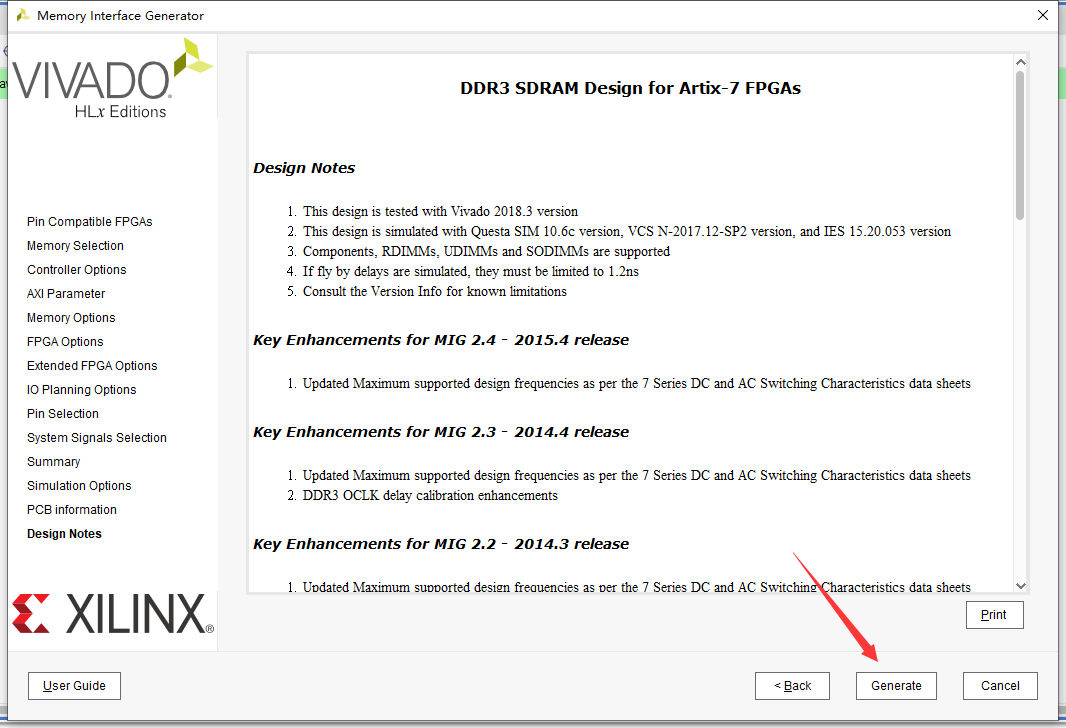

- 3.单击“next”。

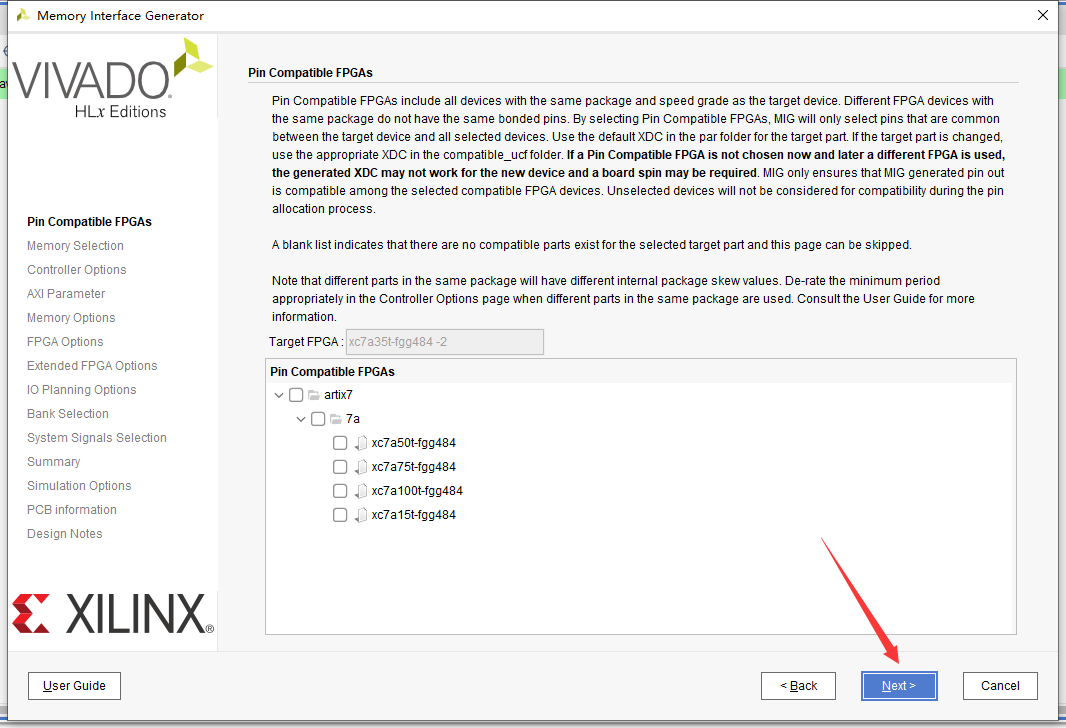

- 4.兼容设置界面,使用默认设置即可。

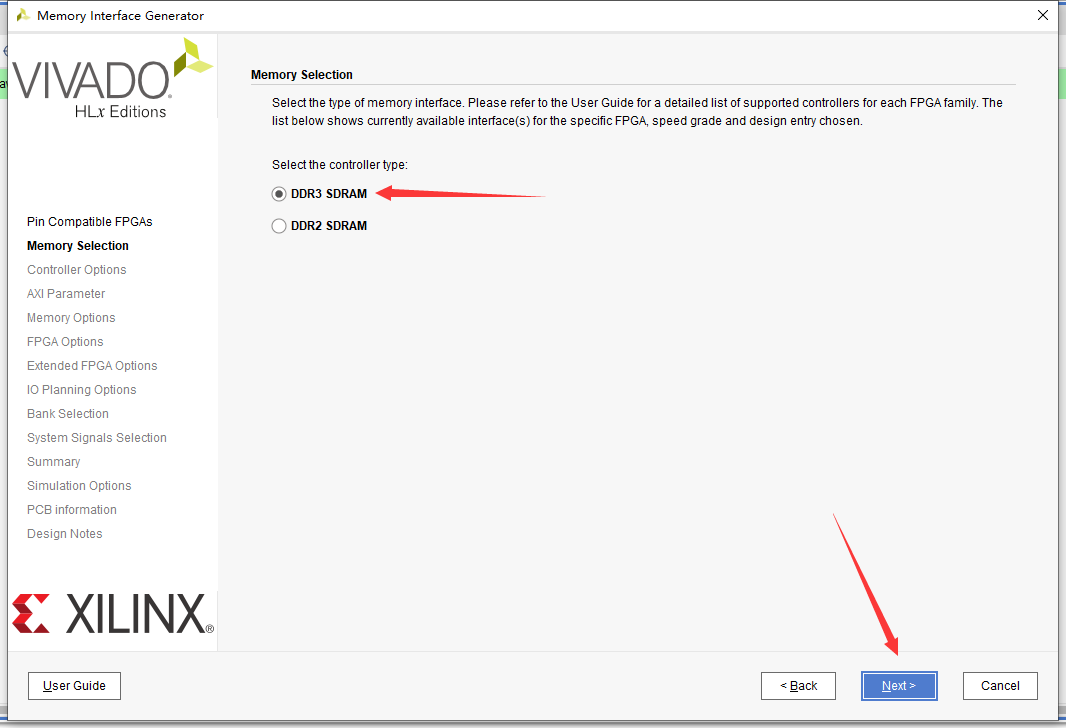

- 5.选择DDR3。

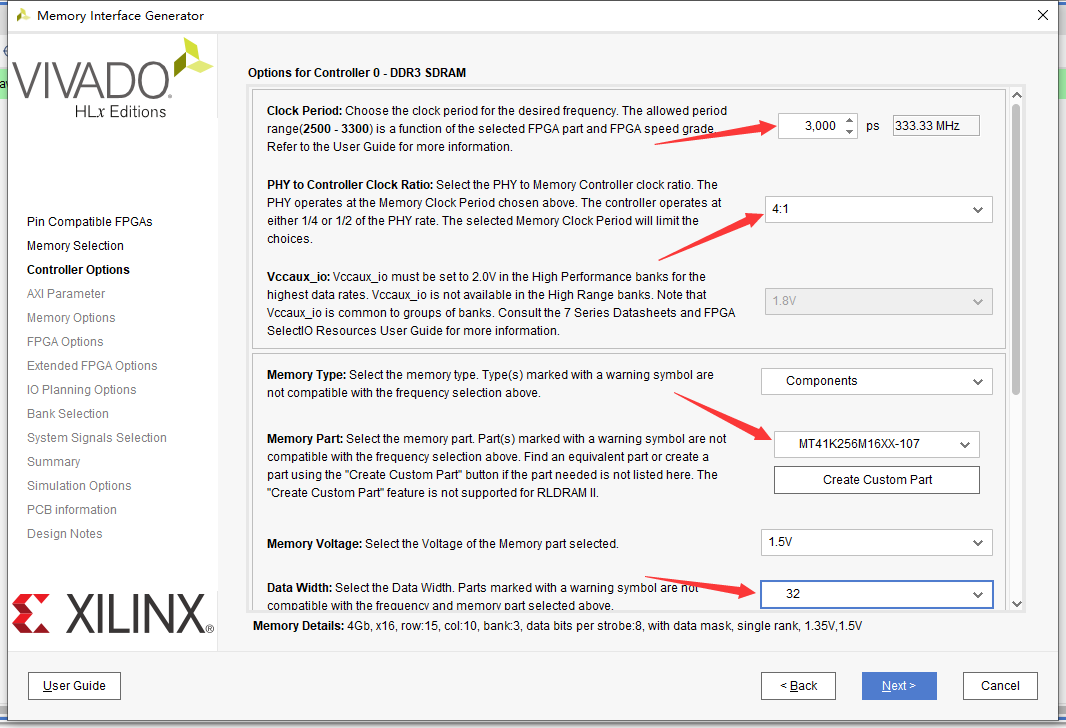

- 6.按照下图所示进行设置。

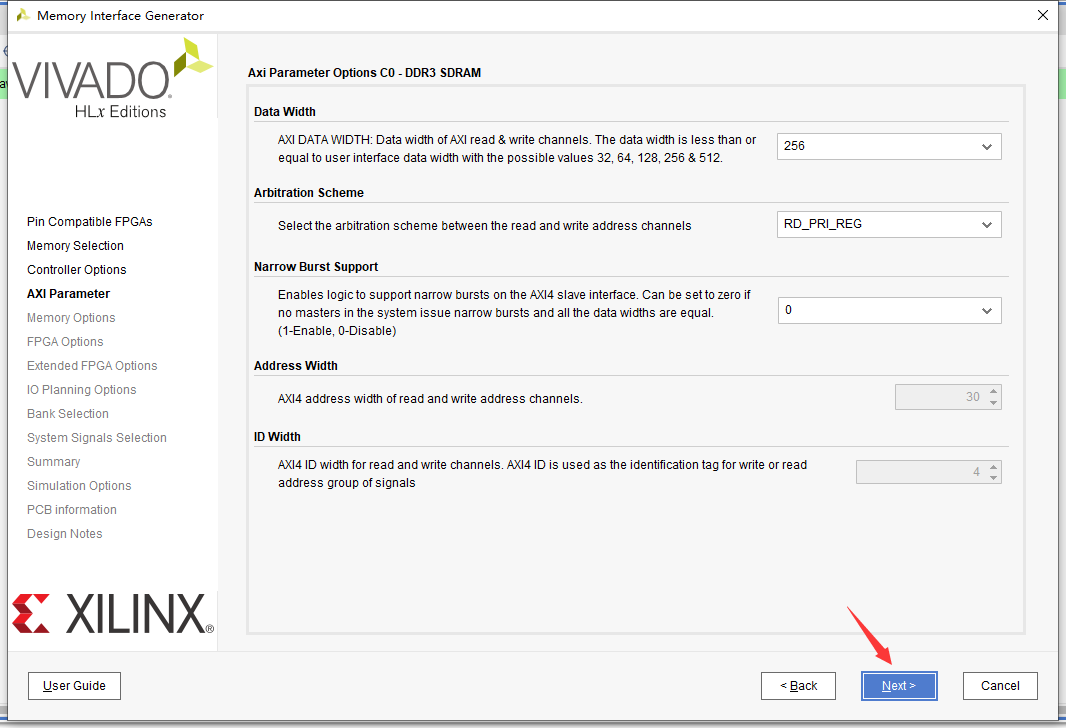

- 7.使用默认设置。

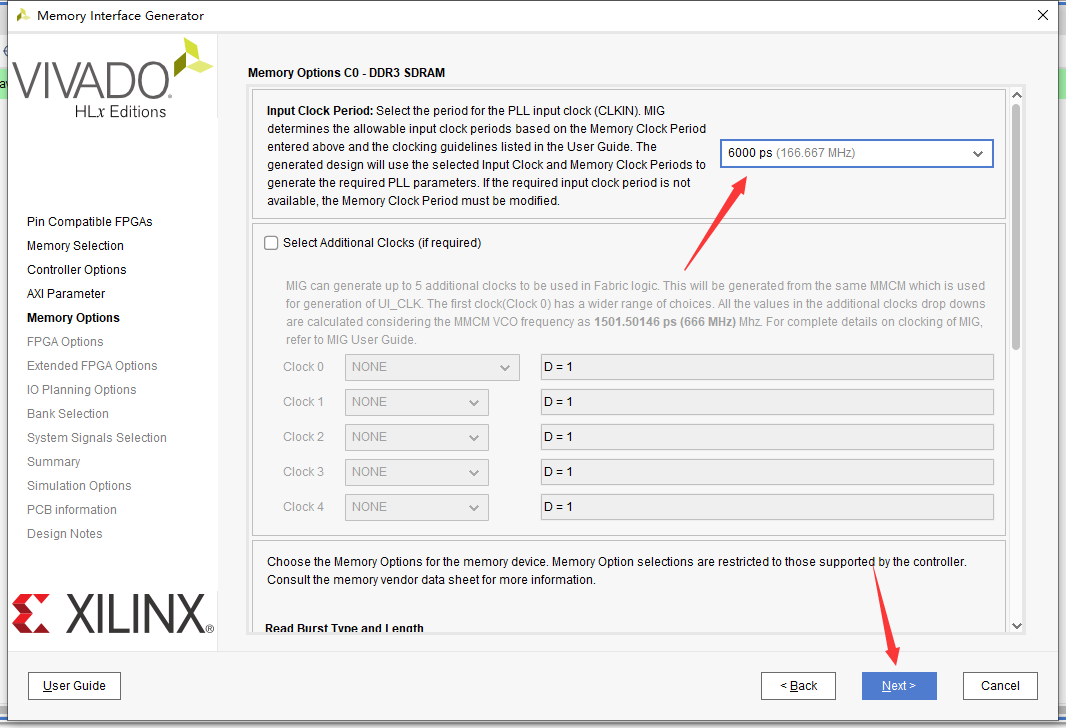

- 8.选择输入时钟频率为166.667MHz,及使用Clocking Wizard模块clk_ou1的时钟。

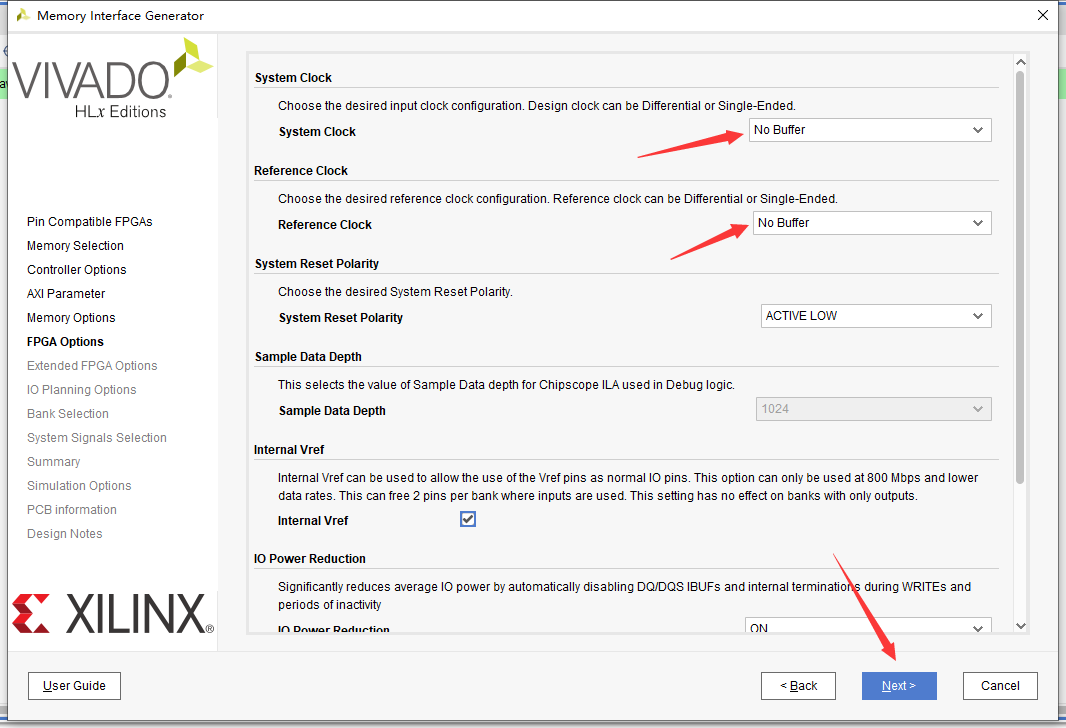

- 9.系统时钟与参考时钟都为No Buffer模式。

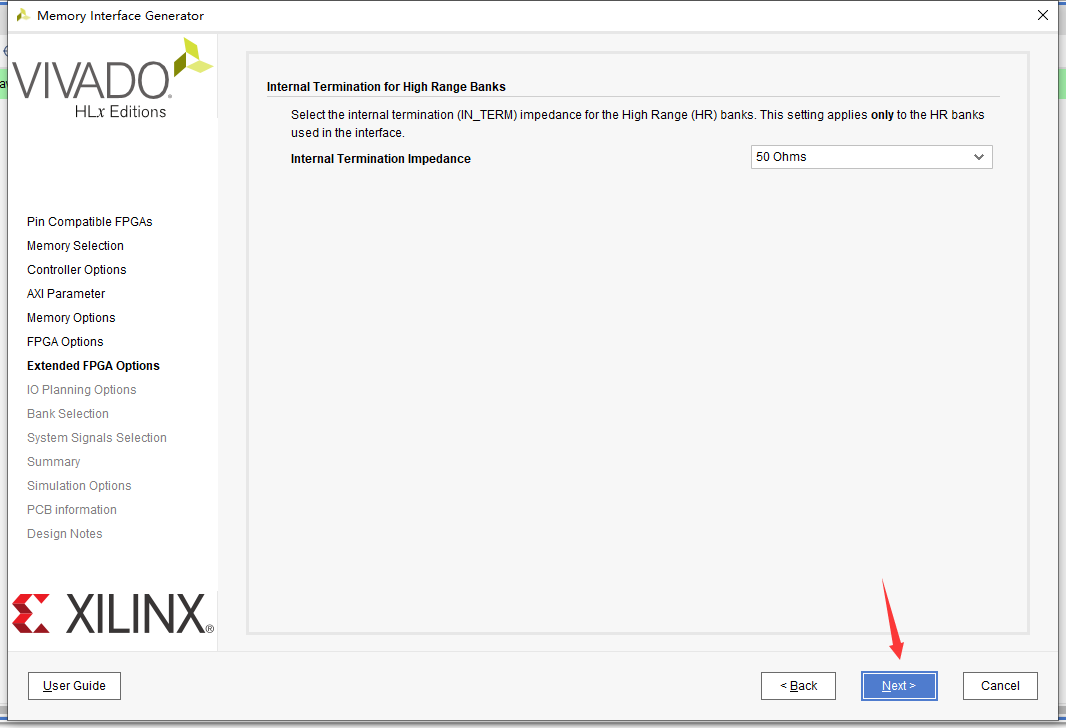

- 10.使用默认设置。

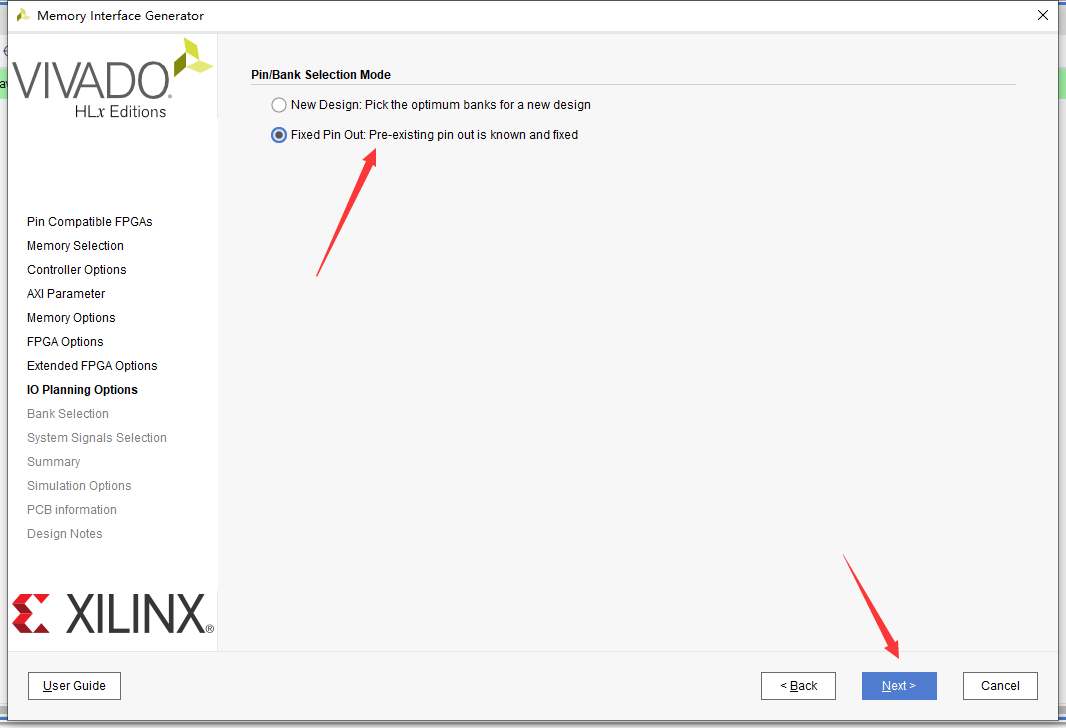

- 11.选择管脚已固定。

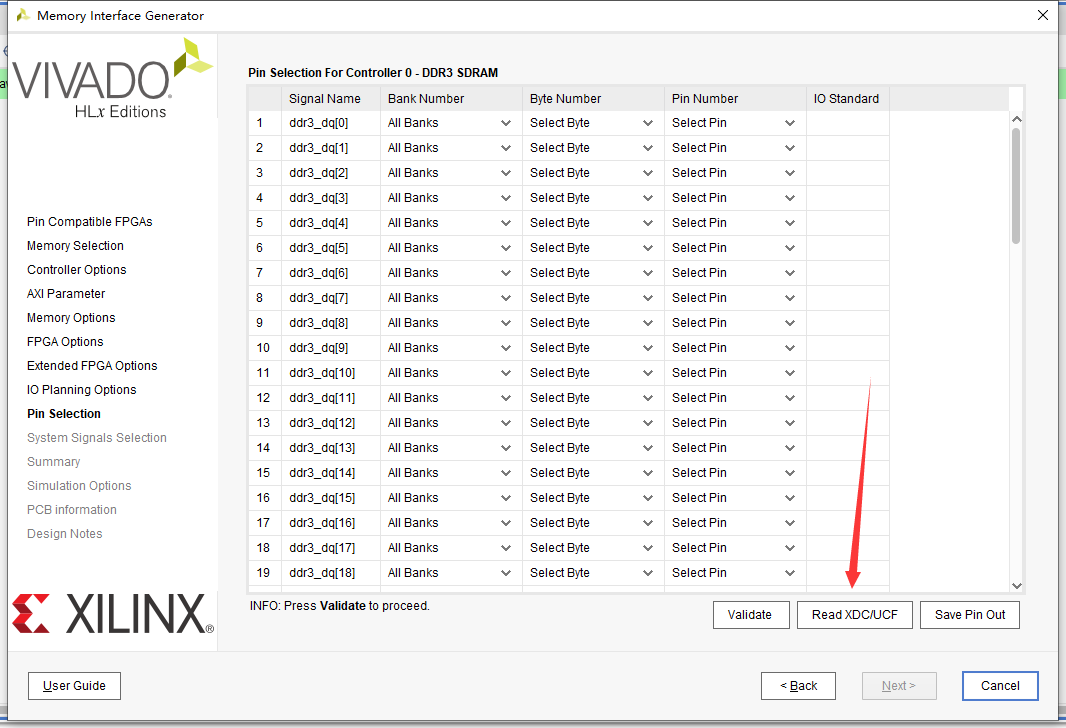

- 12.进入管脚分配界面,选择导入管脚配置文件,若没有管脚配置文件则需手动为每个信号配置引脚。

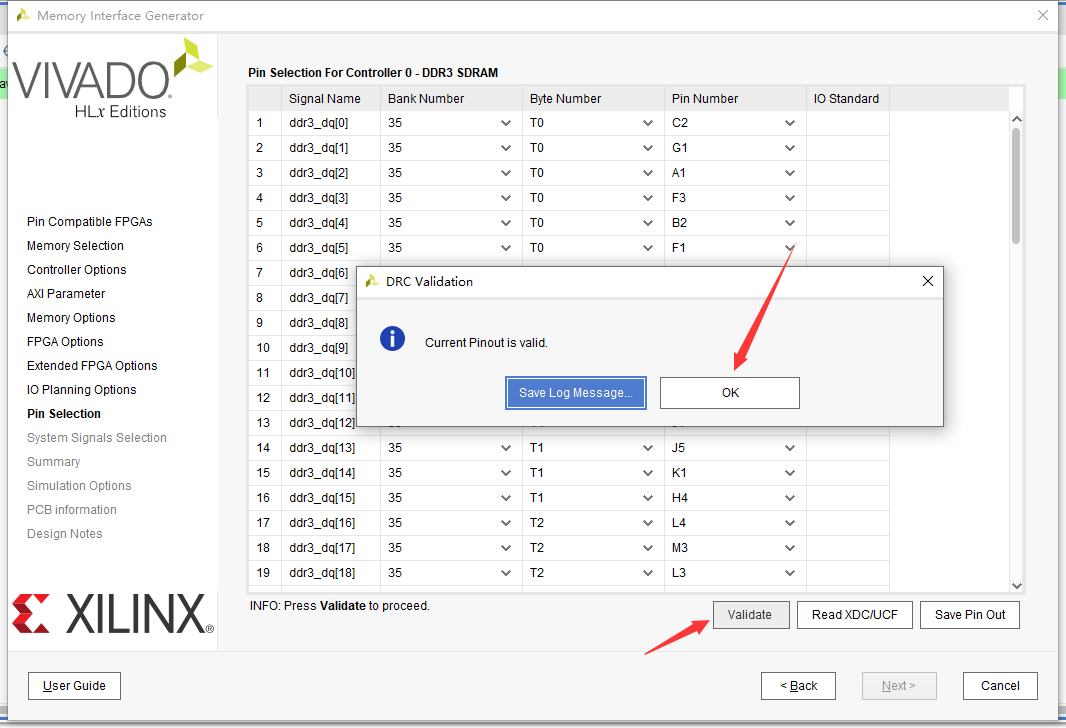

- 13.引脚配置完成后,单击“Validate”,配置验证通过后单击“OK”。如果引脚为手动分配,可以单击“Save Pin Out”保存配置,已便以后使用。单击“Next”进行下一步。

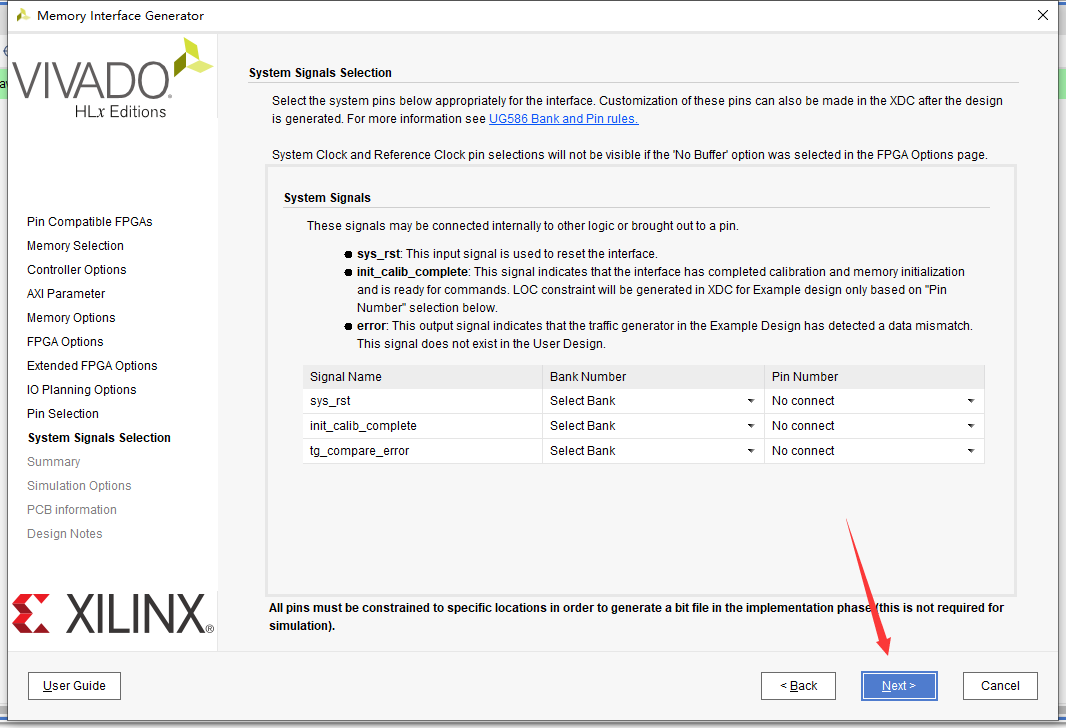

- 14.单击“Next”进行下一步。

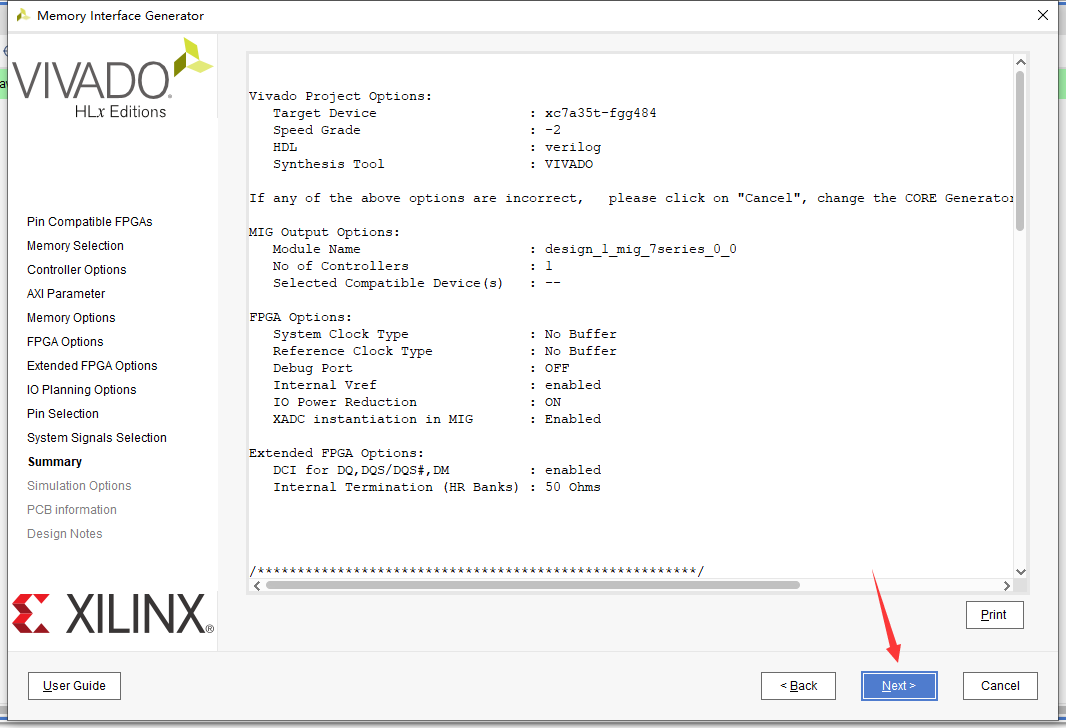

- 15.单击“Next”进行下一步。

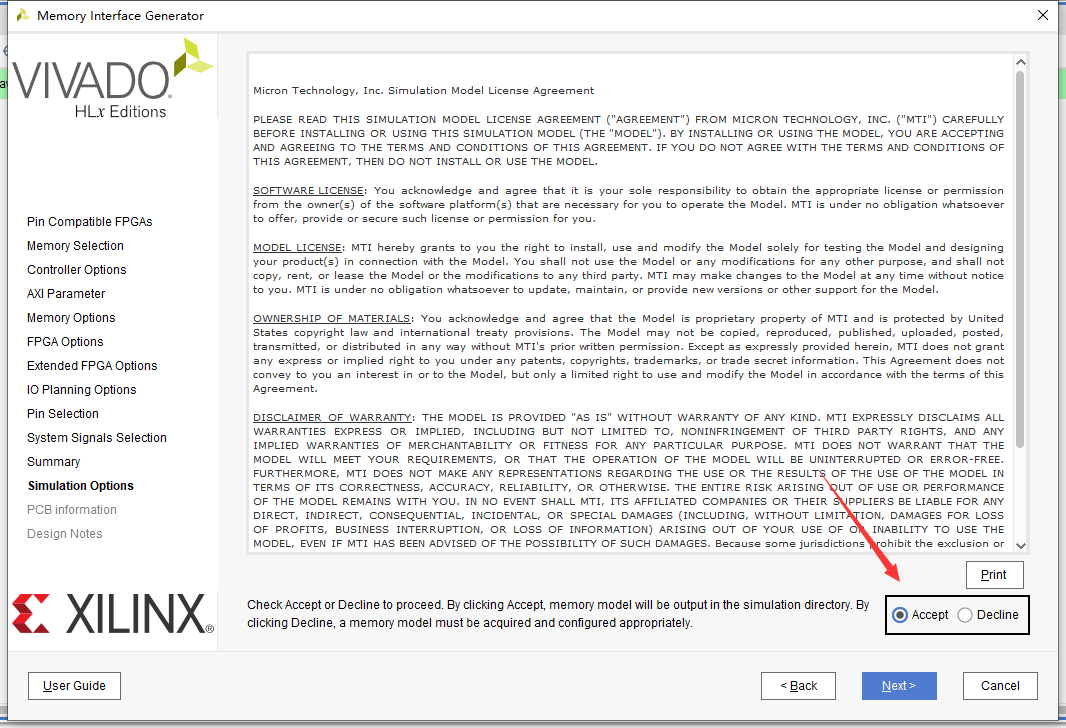

- 16.选择“Accept”,单击“Next”进行下一步。

- 17.单击“Next”进行下一步。

- 18.单击“Generate”完成设置。

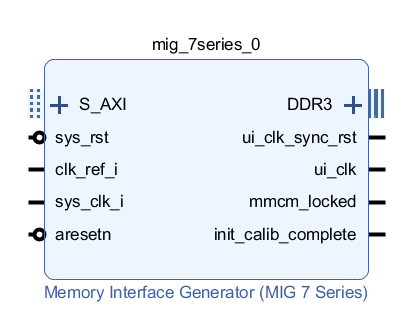

- 19.完成设置后如下图所示。

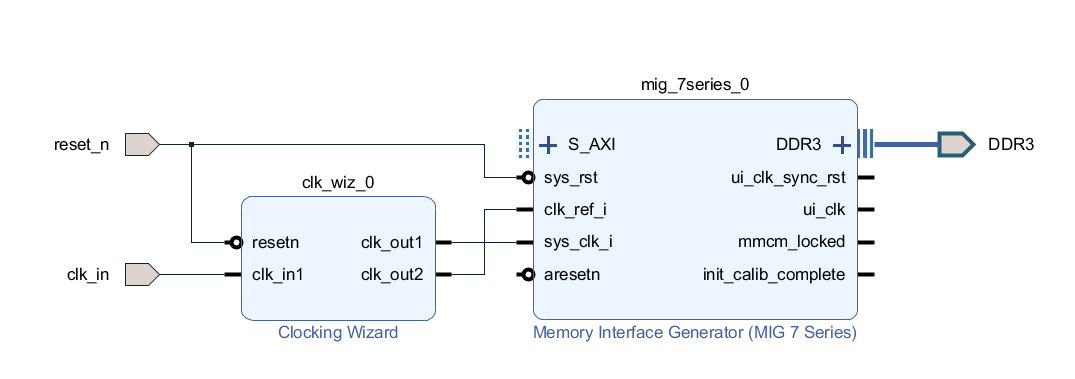

- 20.将复位与时钟模块按照下图所示进行连接,并引出DDR3引脚。

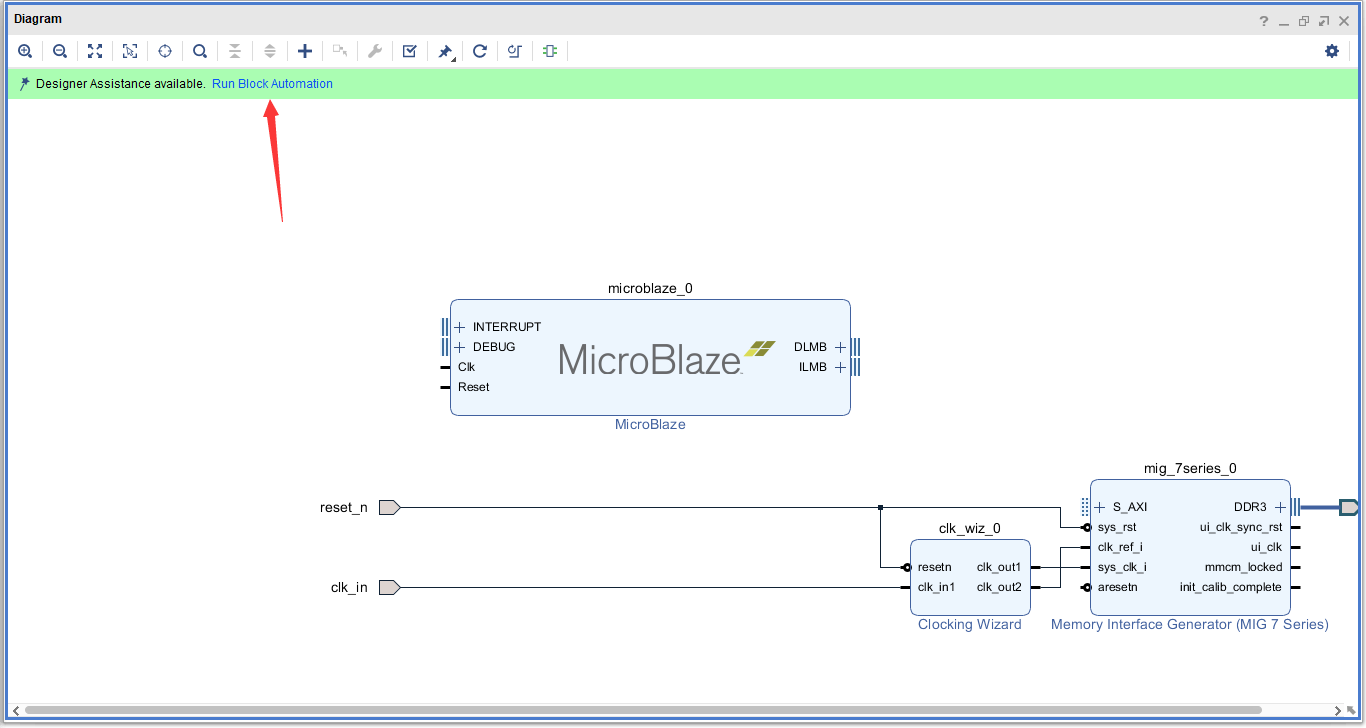

3.添加Microblaze

- 1.添加Microblaze并单击“Run Block Automation”。

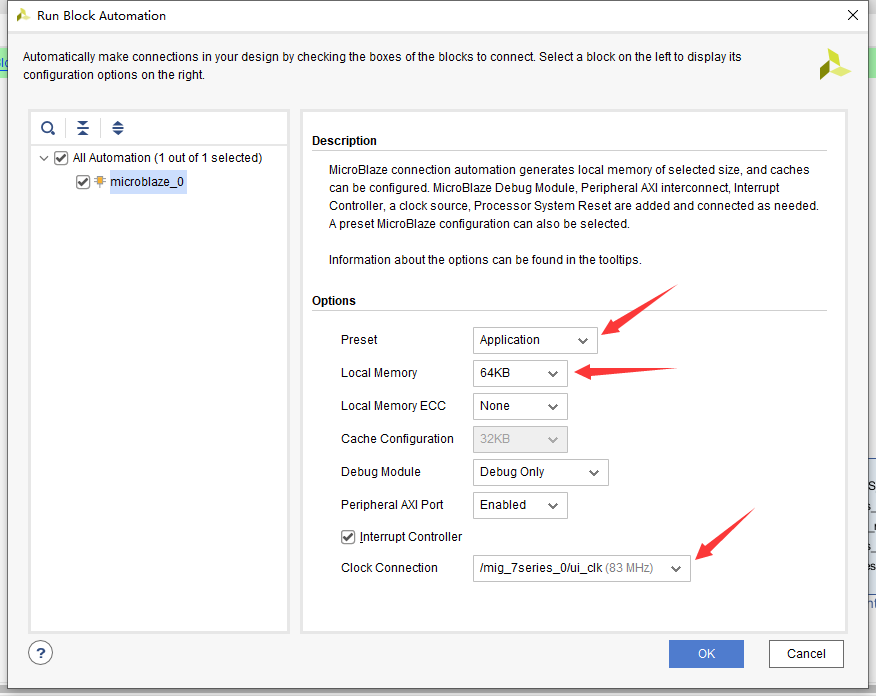

- 2.按照下图所示进行设置,单击“OK”完成配置。

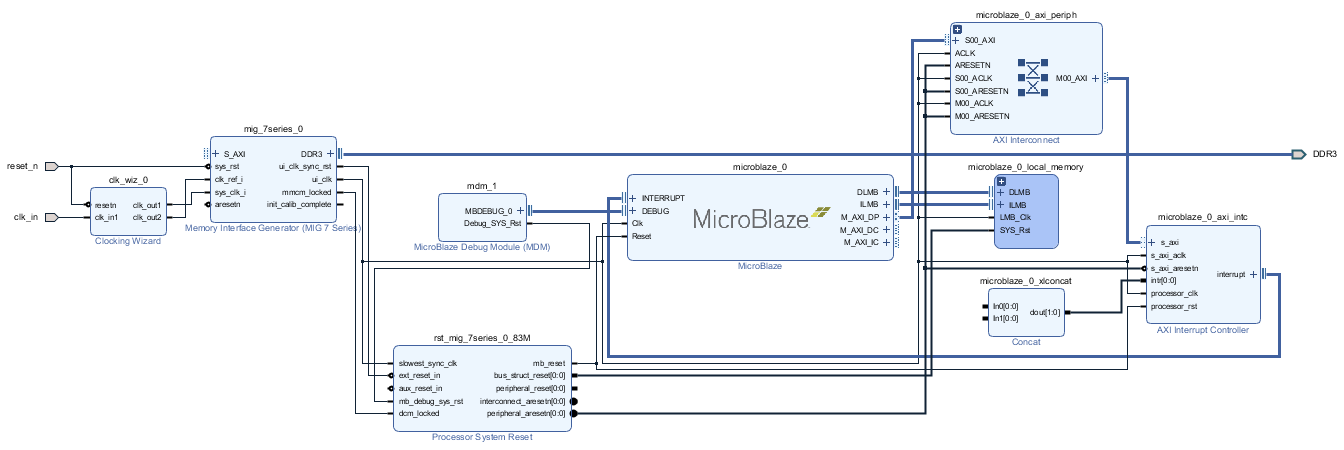

- 3.配置完成后如下图所示。

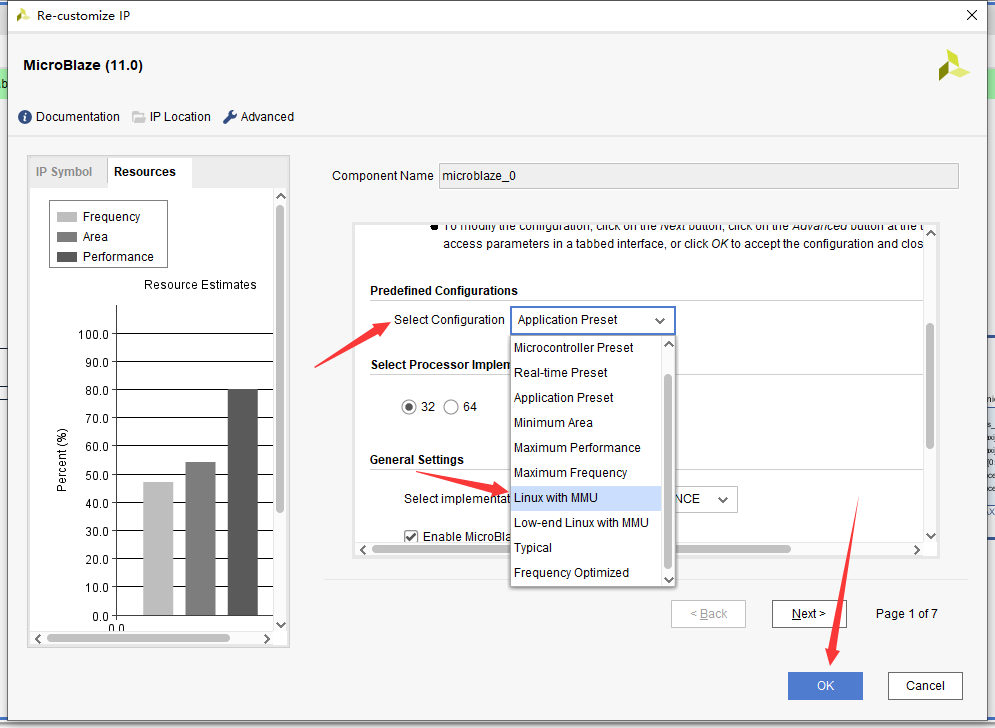

- 4.按照下图所示进行设置,单击“OK”完成配置。

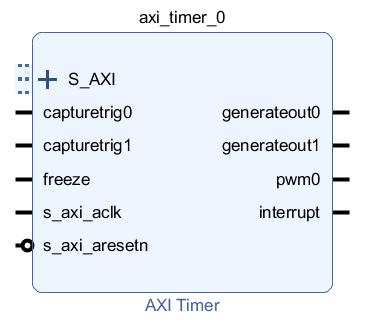

4.添加AXI Timer

- 添加AXI Timer定时器模块。

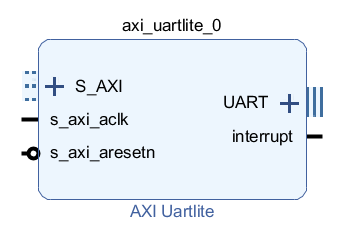

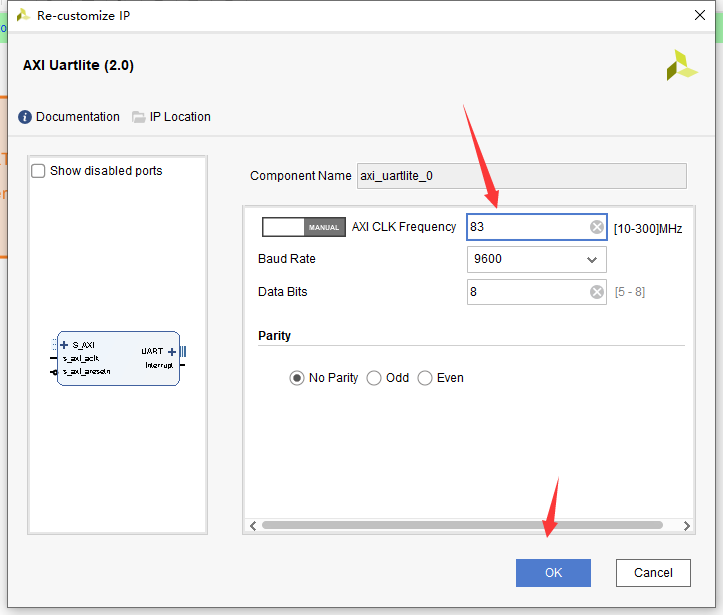

5.添加AXI Uartlite

- 1.添加AXI Uartlite串口通信模块。

- 2.双击该模块,打开设置界面。设置时钟频率为83MHz,单击“OK”完成设置。

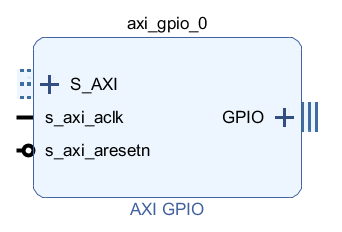

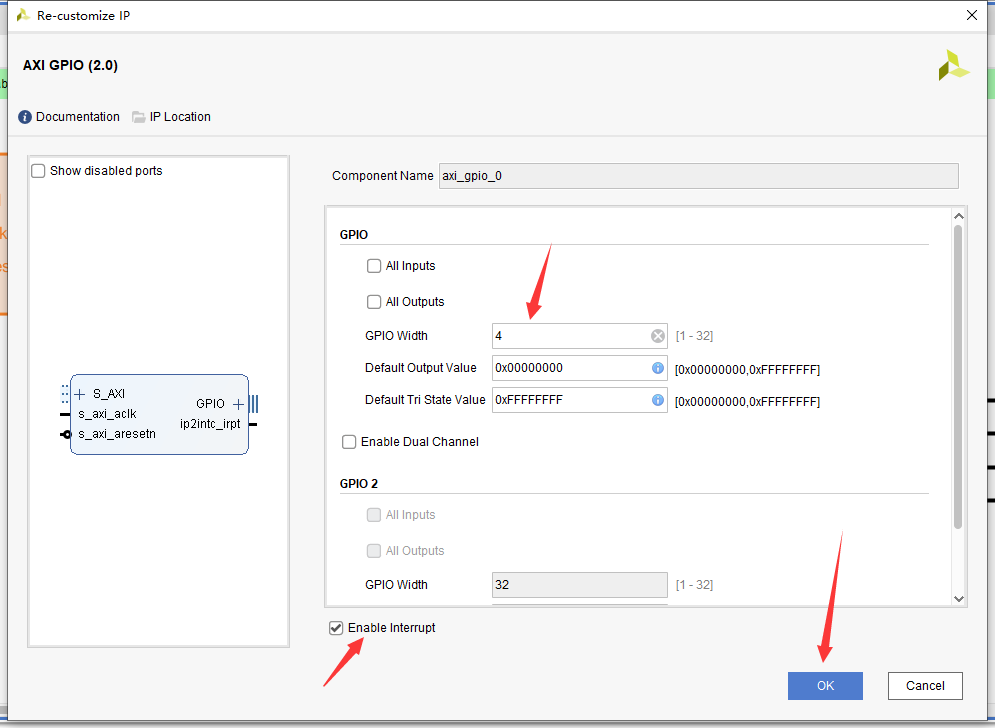

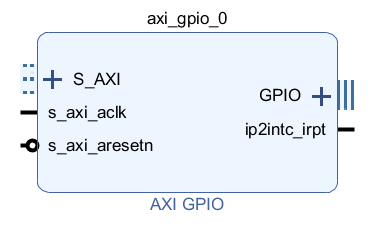

6.添加AXI GPIO

- 1.添加AXI GPIO模块。

- 2.双击该模块,打开设置界面。设置GPIO宽度为4位,使能中断,单击“OK”完成设置。

- 3.设置完成后如下图所示。

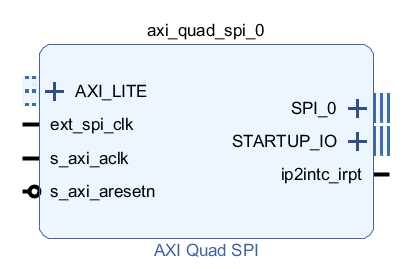

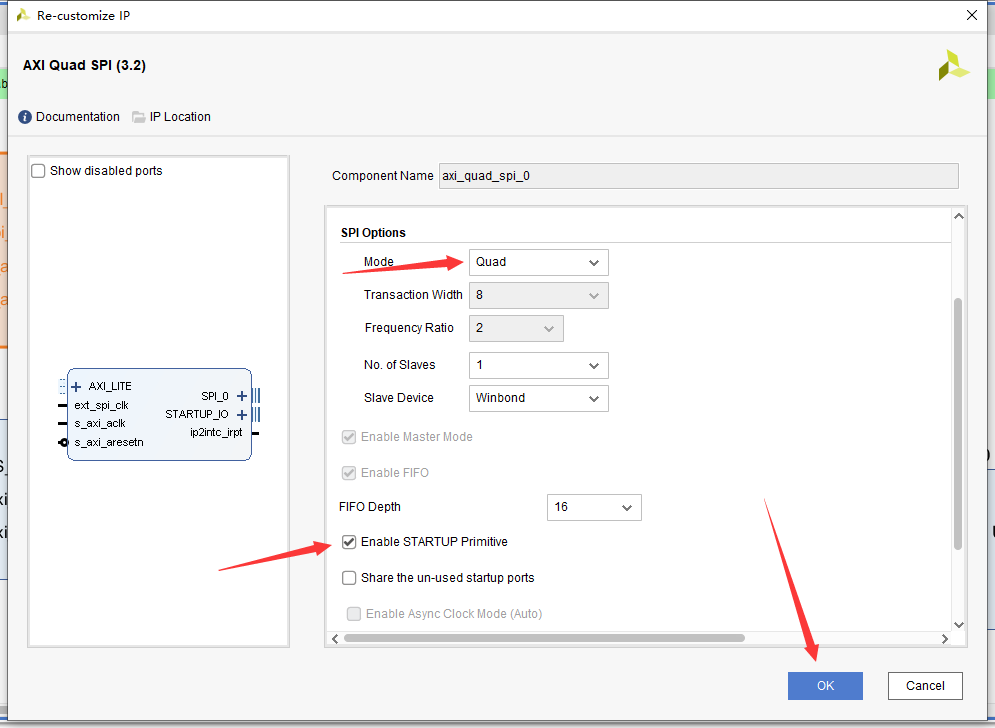

7.添加AXI Quad SPI

- 1.添加AXI Quad SPI模块。

- 2.双击该模块,打开设置界面。设置Mode为Quad,勾选“Enable STARTUP Primitive”,该选项将SPI时钟引脚进行默认分配。单击“OK”完成设置。

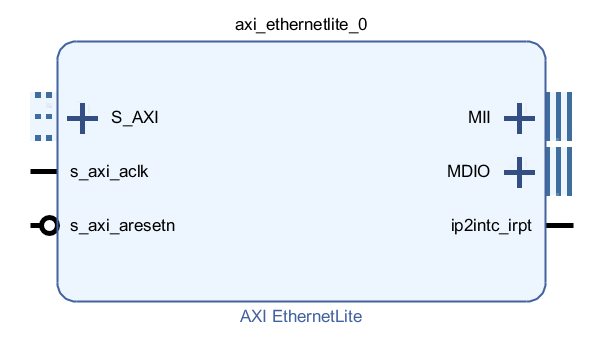

8.添加AXI EthernetLite

- 添加AXI EthernetLite模块。

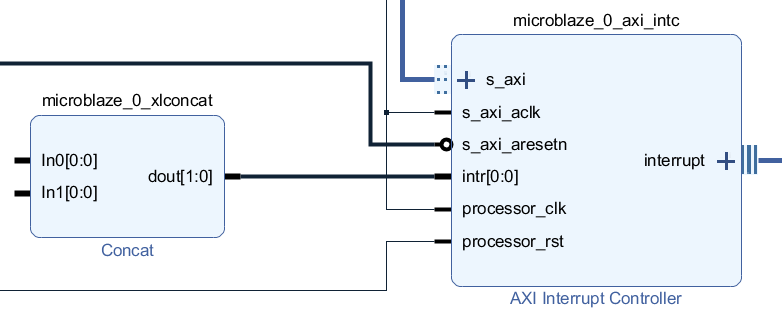

9.中断连接

-

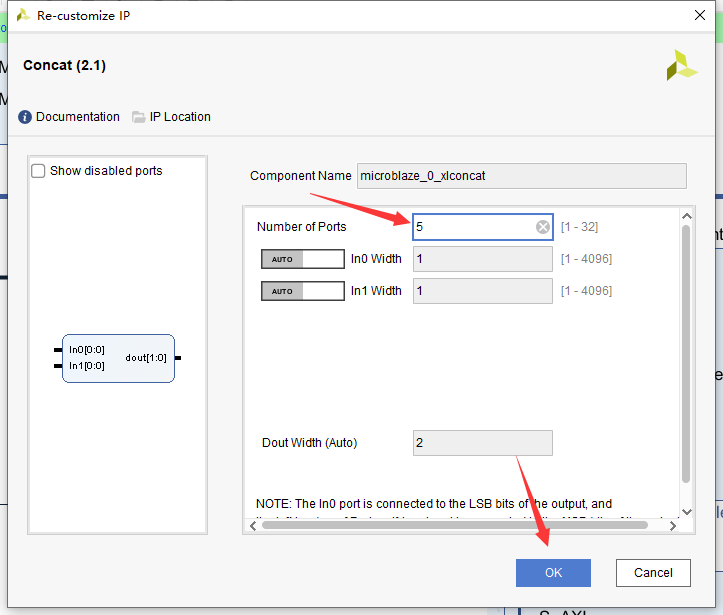

1.双击Concat模块,打开设置界面。

-

2.将输入设置为5,单击“OK”完成设置。

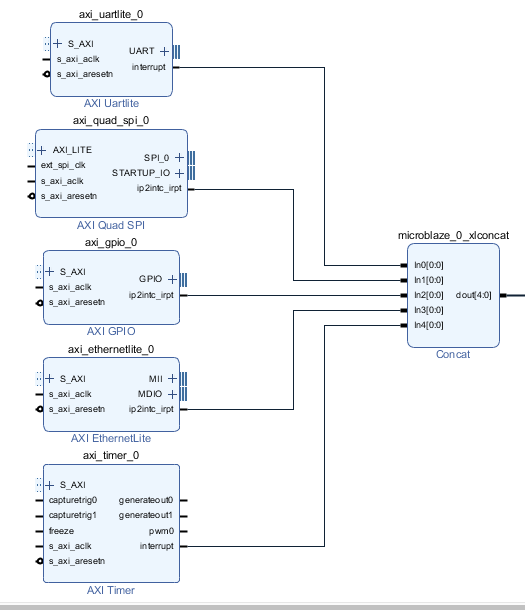

- 3.分别将uart、qspi、gpio、eth、timer模块的中断输出引脚与Concat模块进行连接 。

10.AXI总线连接

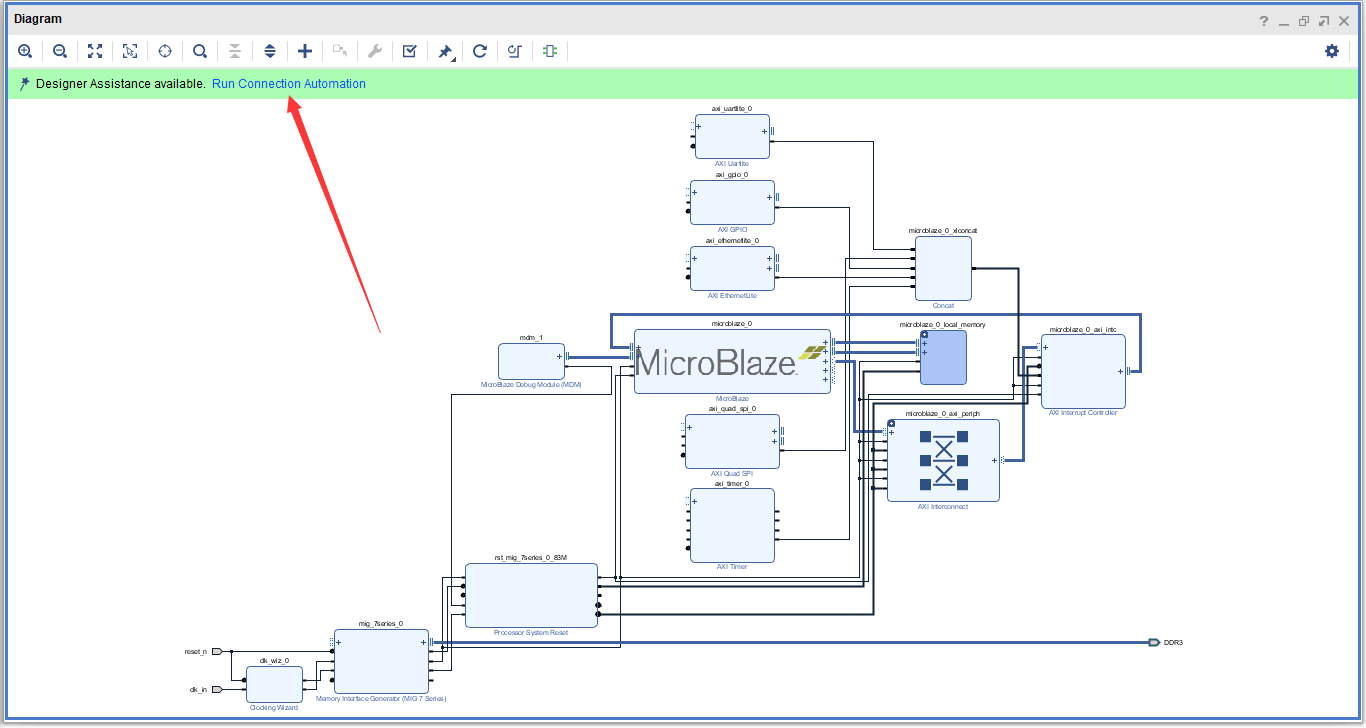

- 1.单击“Run Connection Automation”

- 2.全部勾选,单击“OK”完成设置。

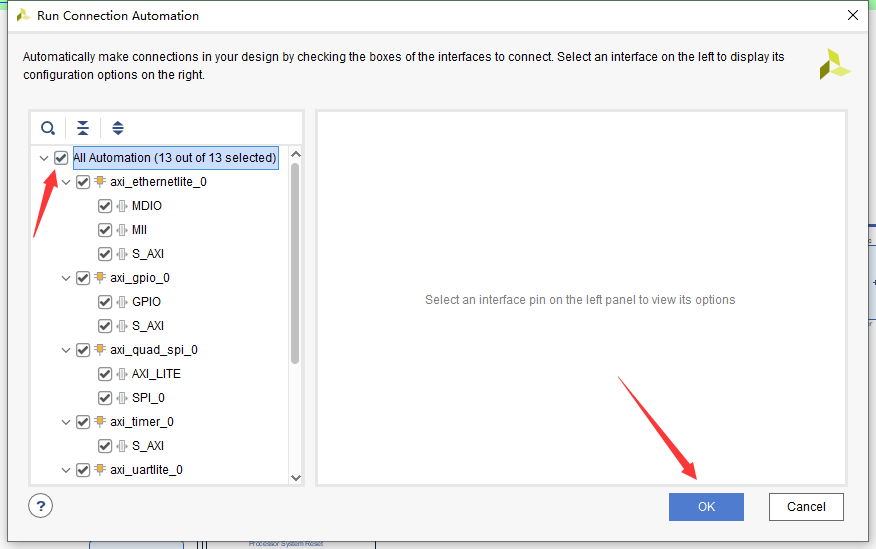

- 4.连接完成后如下图所示。

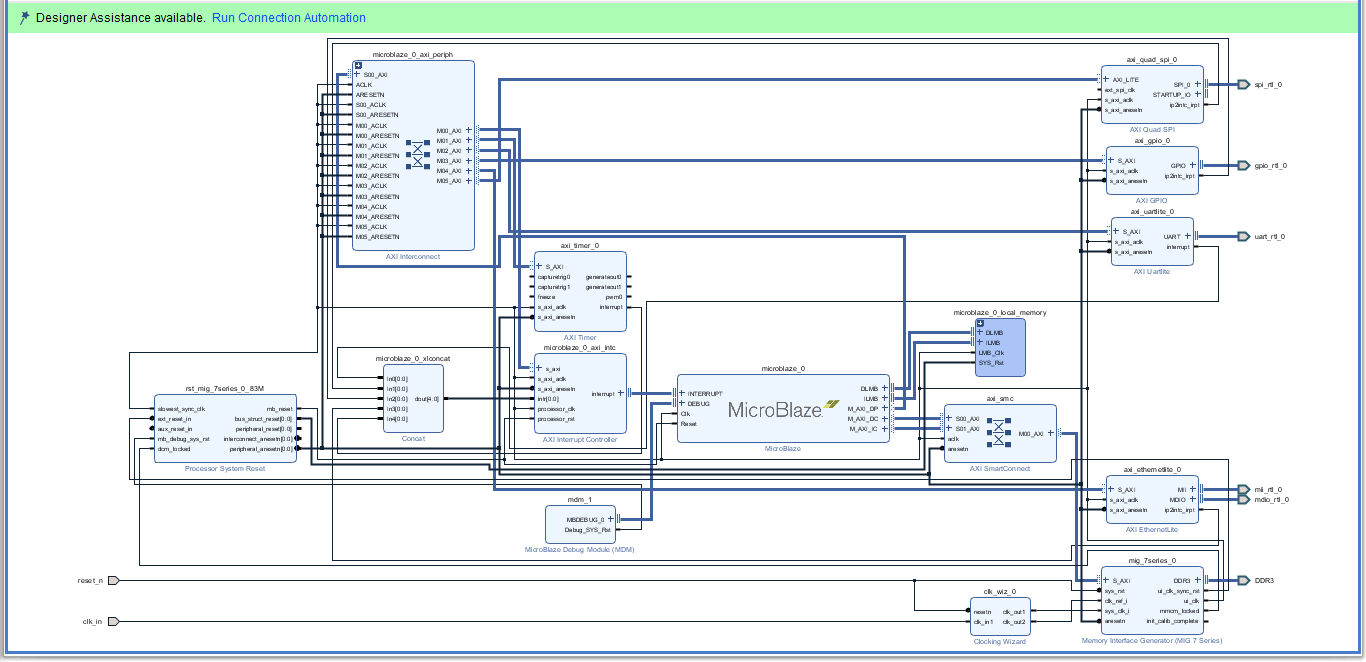

- 4.再次单击“Run Connection Automation”,按照下图所示进行设置,单击“OK”完成设置。

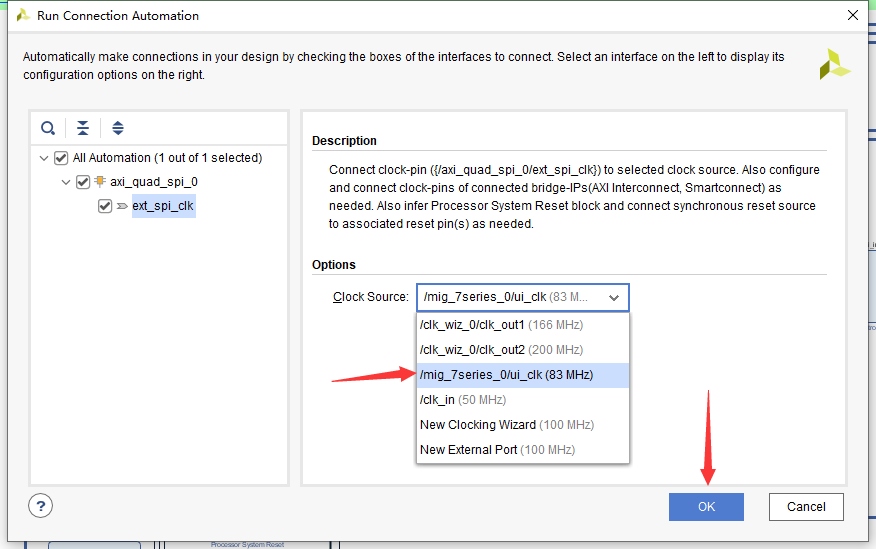

- 5.连接完成后如下图所示。

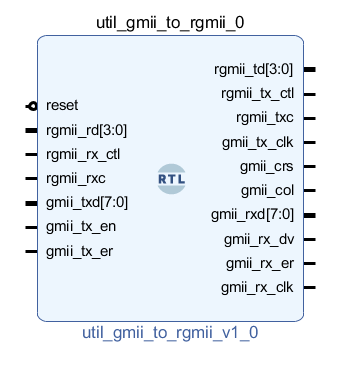

11.添加mii转rgmii模块

由于AXI EthernetLit仅支持速率为10/100M的MII接口,而开发板上的PHY芯片为10/100/1000M的RGMII接口,所以需要将MII接口转为RGMII。

- 1.在工程中添加util_gmii_to_rgmii.v源文件,并将其拖入设计界面。

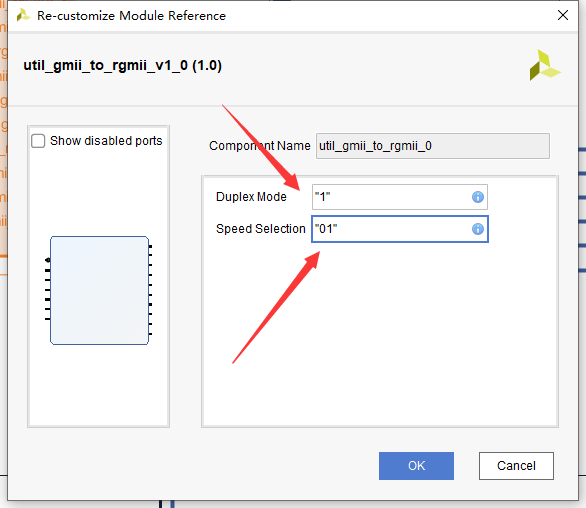

- 2.双击该模块,打开设置界面。设置为全双工,100M。单击“OK”完成设置。

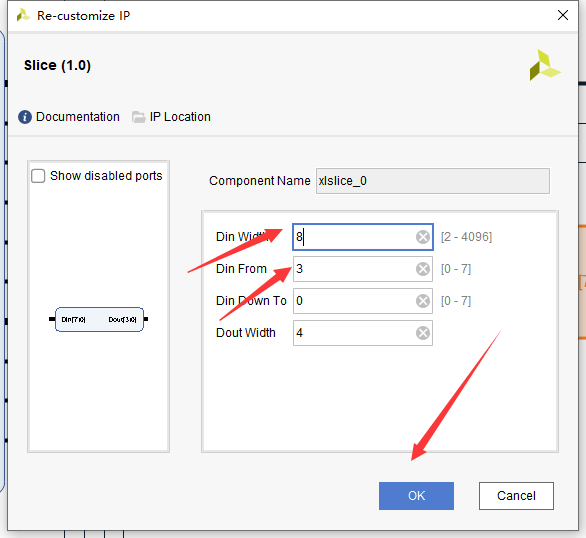

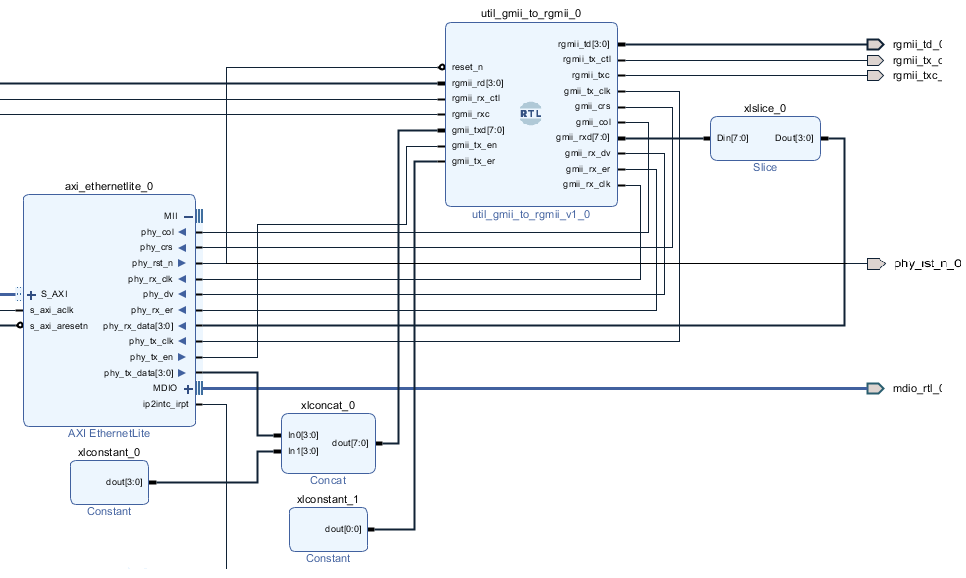

- 3.将AXI EthernetLit模块引出的MII引脚删除,添加Slice模块,并按照下图进行设置。

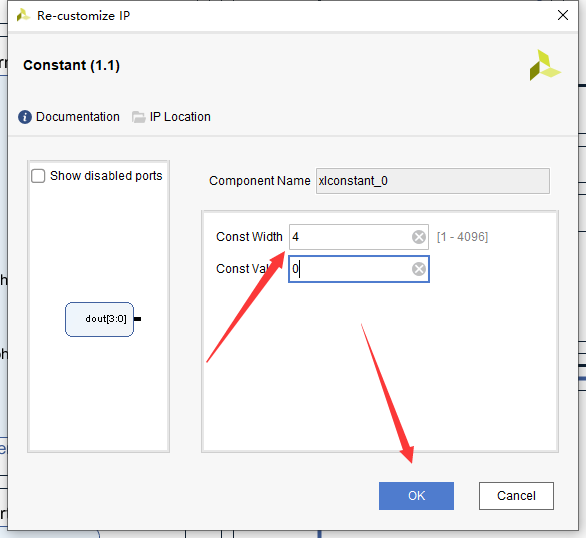

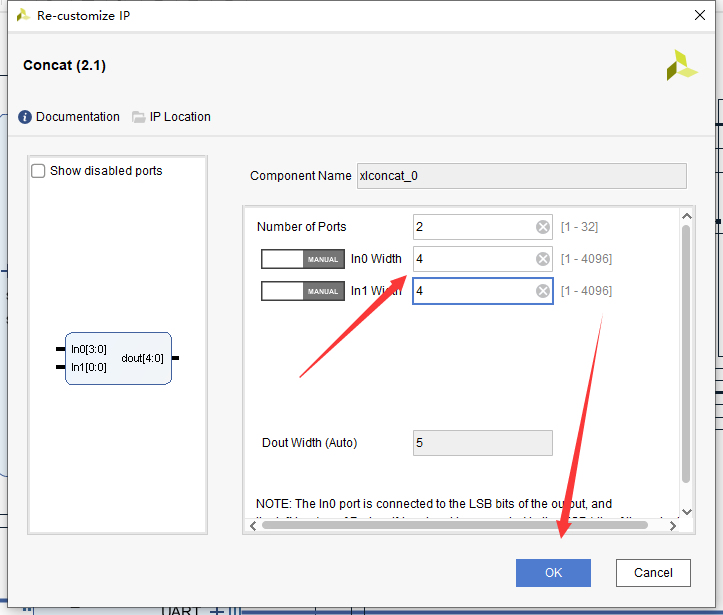

- 4.添加两个Constant模块,并按照下图进行设置。

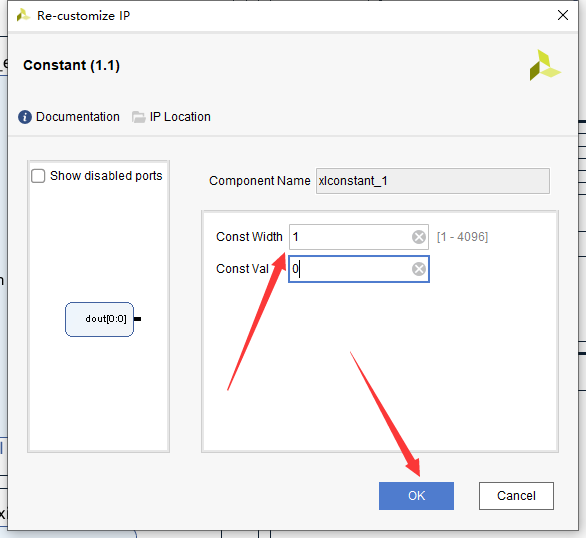

- 5.添加Concat模块,并按照下图进行设置。

- 6.按照下图所示方式进行连接,并引出rgmii_rd,rgmii_rx_ctl,rgmii_rxc,rgmii_td,rgmii_tx_ctl,rgmii_txc,reset_n。

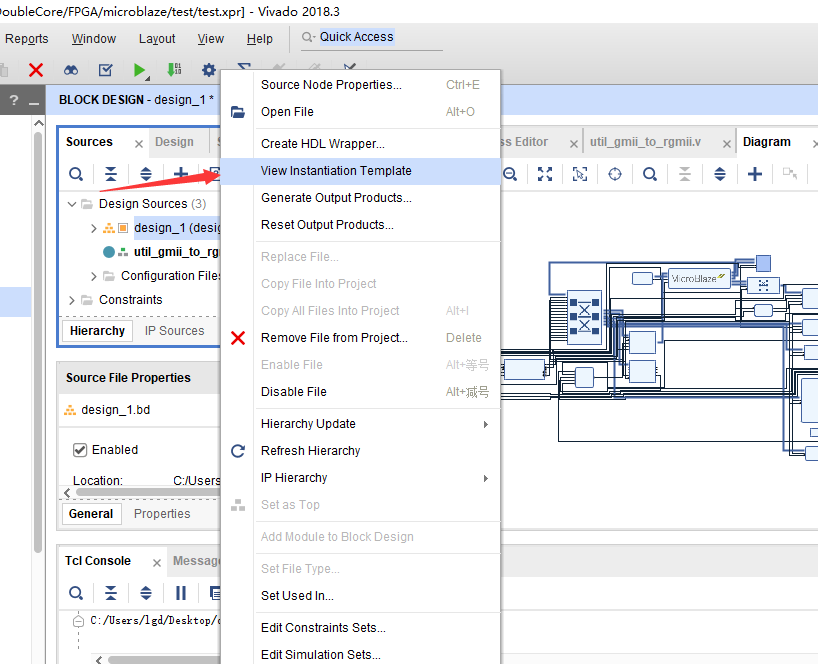

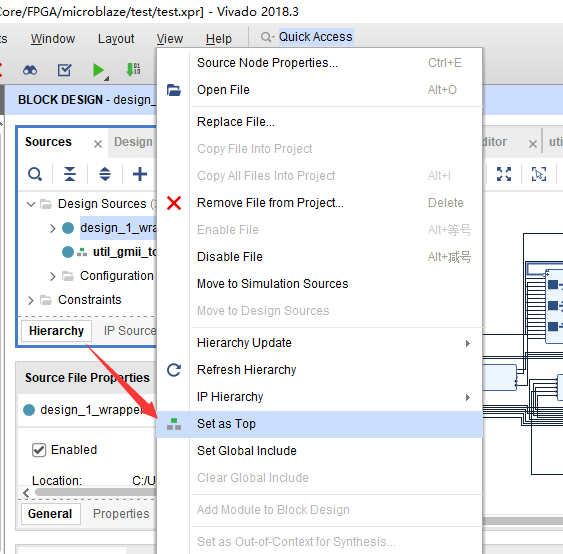

12.导出顶层设计文件

- 1.将所有引出引脚的名称进行修改,然后导出顶层文件。

- 2.将设计设置为顶层。

13.添加引脚约束文件

根据开发板原理图,为每个引出信号分配引脚。

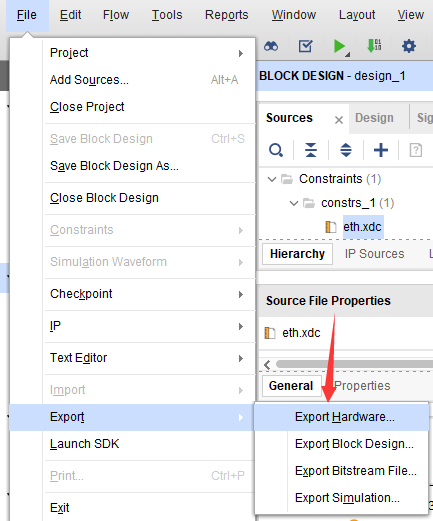

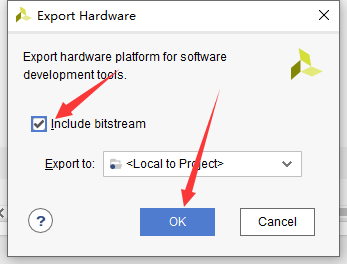

14.生成Bitstream

以上步骤完成后编译生成bit文件。

15.导出硬件描述文件