AXI Stream总线说明和测试

本文主要介绍AXI Stream总线的端口定义、数据传输流程,以及仿真测试结果。同时介绍AXI Stream Interconnect的使用方法,尤其是路由选择。

1 AXI Stream总线介绍

1.1 AXI Stream总线端口定义

本节主要介绍AXI Stream总线各个端口的定义(从Master的角度看,Slave则相反)

1.时钟和复位

| 信号 | 方向 | 说明 |

|---|---|---|

| aclk | input | 时钟,上升沿有效 |

| aresetn | input | 复位, 低电平有效 |

2.写通道

| 信号 | 方向 | 说明 |

|---|---|---|

| tready | input | slave写数据就绪信号 |

| tvalid | output | master写数据有效信号 |

| tdata | output | master写入数据 |

| tkeep | output | master写数据有效位信号 |

| tlast | output | master写入最后一个数据 |

| tuser | output | master写入用户边带数据 |

| tstrb | output | 表示关联数据为Position byte还是Data byte |

| tid | output | 数据Stream ID,表示不同数据流 |

| tdest | output | 为Data Stream提供路由信息 |

| tkeep | tstrb | data type | description |

|---|---|---|---|

| H | H | Data byte | 需要传输的数据字节 |

| H | L | Position byte | 表述数据在数据流中位置的字节 |

| L | L | Null byte | 无效字节 |

| L | H | Reserved | 保留,不强制使用 |

3.读通道

| 信号 | 方向 | 说明 |

|---|---|---|

| tready | output | slave写数据就绪信号 |

| tvalid | input | master写数据有效信号 |

| tdata | input | master写入数据 |

| tkeep | input | master写数据有效位信号 |

| tlast | input | master写入最后一个数据 |

| tuser | input | master写入用户边带数据 |

| tstrb | input | 表示关联数据为Position byte还是Data byte |

| tid | input | 数据Stream ID,表示不同数据流 |

| tdest | input | 为Data Stream提供路由信息 |

1.2 AXI Stream数据传输流程

1.写数据流程

slave在准备好接收数据后,将tready拉高。master在准备好写数据后,拉高tvalid信号,并给tdata、tkeep和tuser赋值,在传输完最后一帧数据后,拉高tlast信号,本次传输结束。

2.读数据流程

slave在准备好读出数据后拉高tready,接收来自master的tvalid、tdata、tkeep和tuser信号,在接收到tlast信号后,结束本次数据传输。

2 AXI Stream总线测试

本节主要介绍对AXI Stream总线所做的测试和对测试结果的分析。

工程源文件:

AXI Stream总线测试工程

2.1 测试工程说明

为了加深对AXI Stream协议的理解,使用Vivado创建测试工程,测试工程的框图如下图所示。

vio

产生写控制信号,

data_gen

模块按AXI Stream协议的要求生成写控制信号和写数据,写入到

axis_data_fifo

模块中。在写入数据完成后,

vio

产生读控制信号,

data_recv

模块从

axis_data_fifo

模块读出数据。通过

ila

模块监控数据传输过程。

2.1.1 写状态机

状态机复位后处于

idle

状态,在接收到start和tready信号后,进入

ready

状态,拉高tvalid信号,并给tdata、tkeep赋值。在计数器计数到最后一帧数据时,拉高tlast信号,进入

last

状态,在完成最后一帧数据传输后,进入

idle

状态。在tready信号无效后进入

susp

状态,暂停数据传输,在tready信号恢复有效后,数据传输也恢复。

2.1.2 读状态机

状态机复位后处于

idle

状态,在接收到start信号后拉高tready信号,开始接收来自master的tvalid、tdata、tkeep和tuser信号,在接收到tlast信号后,结束本次数据传输。

2.2 测试结果分析

2.2.1 仿真波形

2.2.2 写数据波形图

2.2.3 读数据波形图

3 AXI Stream Interconnect说明

3.1 IP介绍

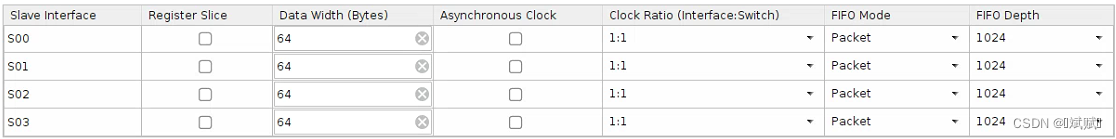

AXI Stream Interconnect可以将多个AXI Stream通道汇聚成一个,也可以将一个AXI Stream通道发散为多个,尤其是可以通过TDEST的信号选择输入的信号从哪个通道输出,IP的设置界面和输入输出端口如下图所示。

-

Arbiter Type

- Round-Robin:对每个Slave端口采用轮询的方式。

- Fixed:S00的优先级最高,S01次之,以此类推。

- Arbitrate on TLAST transfer:如果勾选,传输会在上一个通道的所有数据都传输完成后(tlast信号),才会结束这个通道的传输,开始传输下一个获得仲裁的通道的数据。

- Arbitrate on maximum number of transfers:在传输完设置次数的数据后,switch放弃控制,其它通道可获得传输数据的权限。

- Arbitrate on number of LOW TVALID cycles:如果一个通道获得传输数据的权限,但它传输的次数没到Arbitrate on maximum number of transfers设置的次数,在tvalid信号有指定数量的低电平后,其它通道可获得传输数据的使用权。

-

Slave Interface

- Register Slice:有时序问题时可以使能。

- Asynchronous Clock:有异步时钟的时候需要使能,使能后会添加时钟转换模块。

- Clock Ratio:同步时钟设置时钟比例。

-

FIFO Mode:

- Disabled:无FIFO

- Normal:正常FIFO,与Register Slice效果一致。

- Packet:存储完一帧数据(tlast信号)后开始数据传输。

- FIFO Depth:FIFO深度。

- Connectivity:互联设置

- Routing:路由设置

3.2 IP测试

创建

IP的测试工程

,输入一个信号,通过TDEST信号进行输出通道的选择,仿真结果如下图所示。