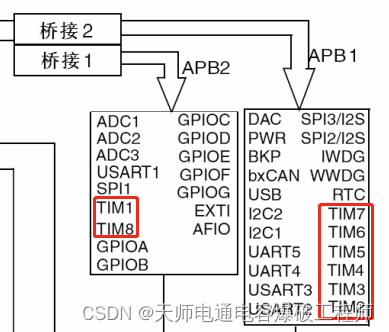

STM32F103RCT6上总共有8个定时器,其中TIM1和TIM8是高级定时器,它们挂载在APB2高速总线上。而TIM2、TIM3、TIM4、TIM5是通用定时器,TIM6、TIM7是基本定时器,它们都挂载在APB1上,基本定时器的功能最少,高级定时器功能最多。所以以学习通用定时器为主。

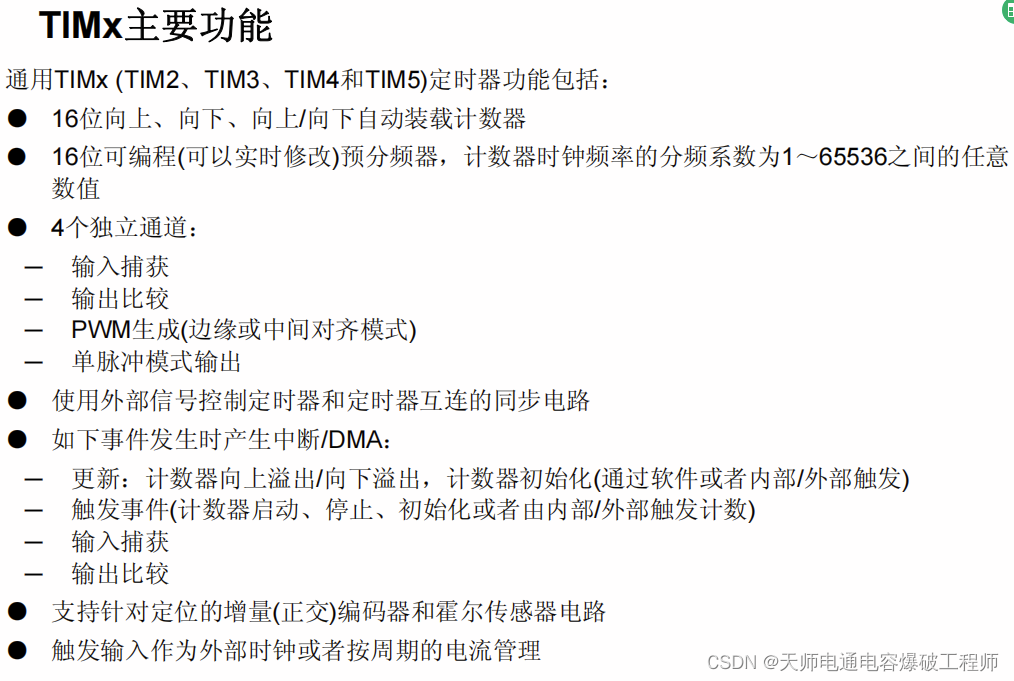

通用定时器的功能

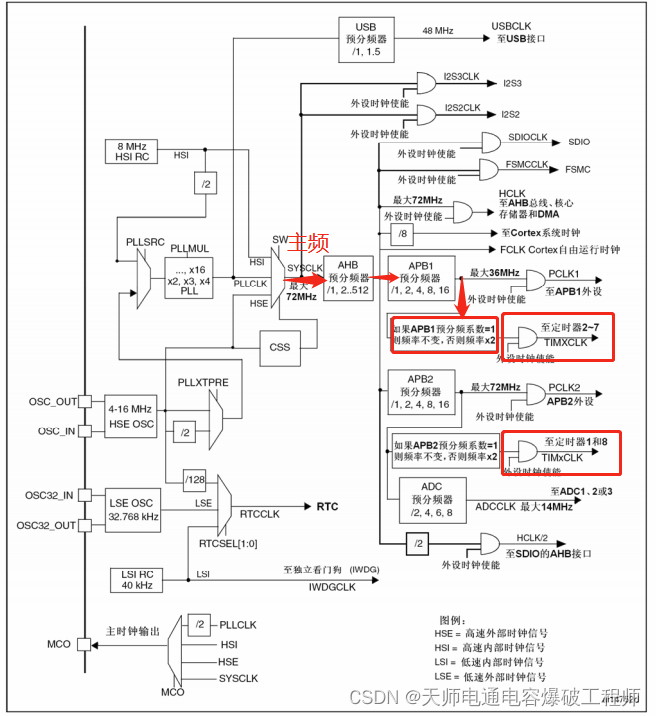

定时器的时钟输入

需要参考手册第二章存储器和总线架构,第六节的时钟树

假设 主频设置了最高的72Mhz,因为APB1的时钟最大是36Mhz,所以在APB1预分频器上就需要分频,预分频系数为2,则APB1的时钟就是36Mhz了,又因为手册说如果APB1预分频系数不是1,则频率x2之后给定时器2~7。也就是会给72Mhz的时钟给定时器2~7;

假设 主频设置的是36Mhz,在APB1预分频器里不分频,那么APB1的时钟就是36Mhz。又因为APB1的预分频系数=1,则频率不变直接给到定时器2~7。也就是会给36Mhz的时钟给定时器2~7

所以想要使用定时器,一定要先配置好主频。野火的sys.c中已经有初始化时钟的函数了。

//系统时钟初始化函数

//pll:选择的倍频数,从2开始,最大值为16

void Stm32_Clock_Init(u8 PLL)

{

unsigned char temp=0;

MYRCC_DeInit(); //复位并配置向量表

RCC->CR|=0x00010000; //外部高速时钟使能HSEON

while(!(RCC->CR>>17));//等待外部时钟就绪

RCC->CFGR=0X00000400; //APB1=DIV2;APB2=DIV1;AHB=DIV1;

PLL-=2; //抵消2个单位(因为是从2开始的,设置0就是2)

RCC->CFGR|=PLL<<18; //设置PLL值 2~16

RCC->CFGR|=1<<16; //PLLSRC ON

FLASH->ACR|=0x32; //FLASH 2个延时周期

RCC->CR|=0x01000000; //PLLON

while(!(RCC->CR>>25));//等待PLL锁定

RCC->CFGR|=0x00000002;//PLL作为系统时钟

while(temp!=0x02) //等待PLL作为系统时钟设置成功

{

temp=RCC->CFGR>>2;

temp&=0x03;

}

} PLL填9,选择9倍频,晶振8Mhz,就可以得到主频72Mhz,这个函数会配置APB1预分频系数为2,APB1得到36Mhz时钟。

版权声明:本文为qq_42697289原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。