并行加法器的快速进位

一、并行进位

1、原因

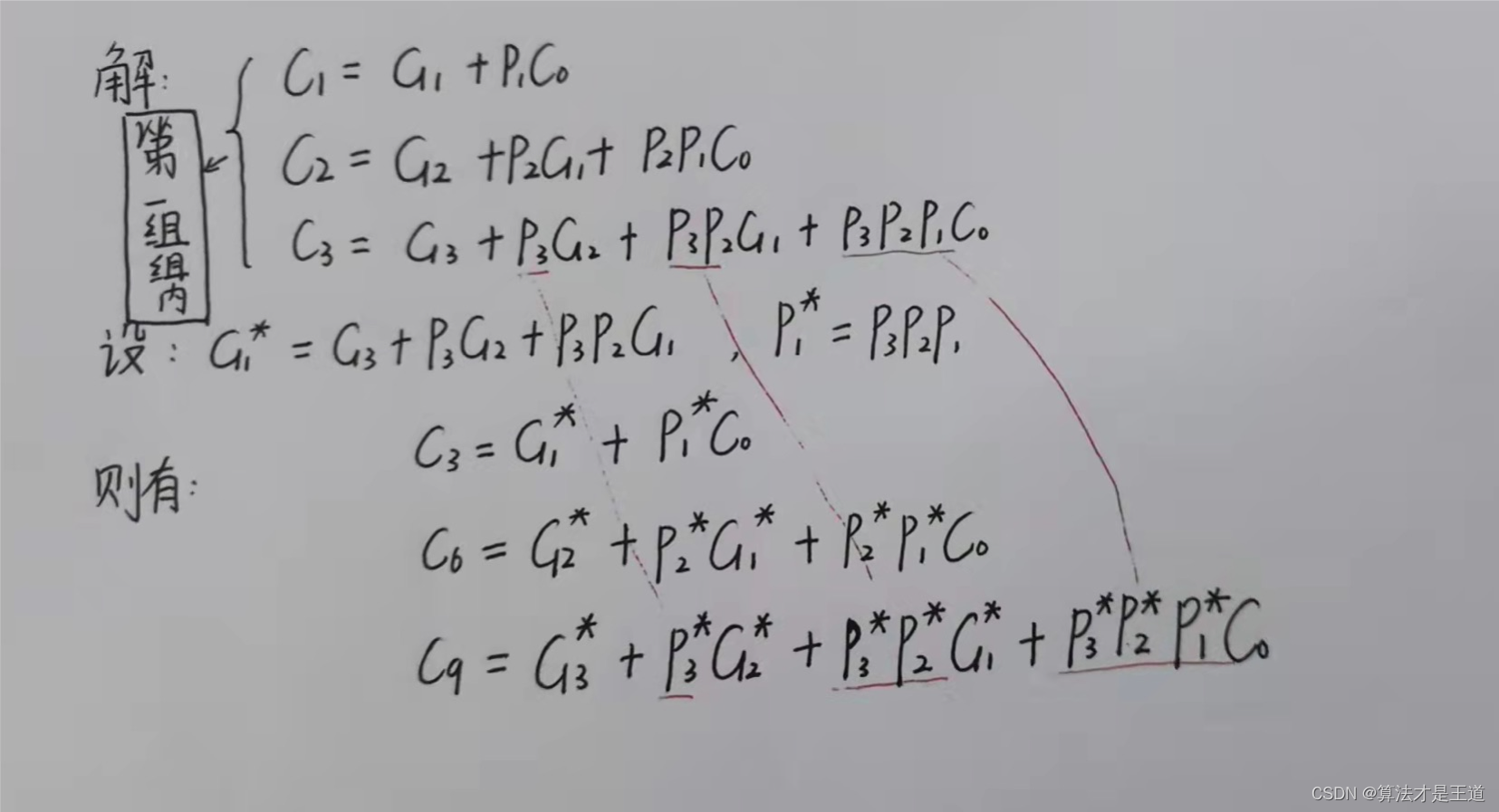

由于串行进位的延迟时间太长,因为串行进位的每一级进位都是依赖于前一级的。(比如C1 = G1+P1C0,C2 = G2 + P2C1,在这里C2是依赖于C1的)

2、定义

并行进位又称为先行进位、同时进位,其特点是

各级进位信号同时形成

。

比如:C1 = G1+P1C0,C2 = G1+P2G1+P2P1C0

C1和C2都是同时产生的,因为它们都只依赖于C0,C0同时打入,C1和C2就同时产生。

3、缺点

随着加法器位数不断增加,Ci的表达式会越来越长,这会使电路变得很复杂,所以完全采用并行进位是不现实的。

二、分组并行进位

这种进位方式是把n位字长分为若干小组,

在小组内

采用并行进位,

在小组间

既可以串行进位,又可以并行进位。

1、单级先行进位方式(组内并行,组间串行)

2、多级先行进位方式(组内并行,组间并行)

三、 练习题

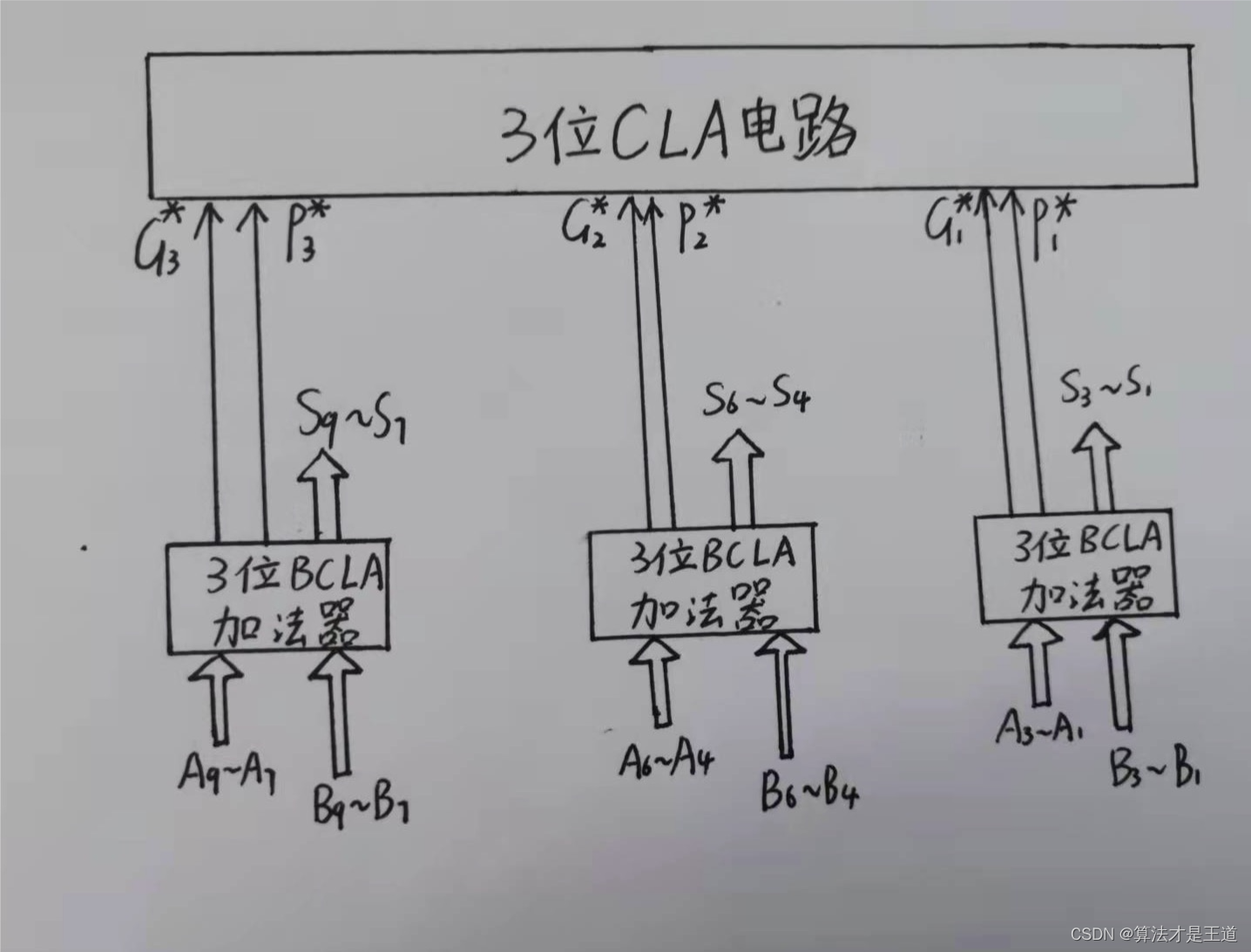

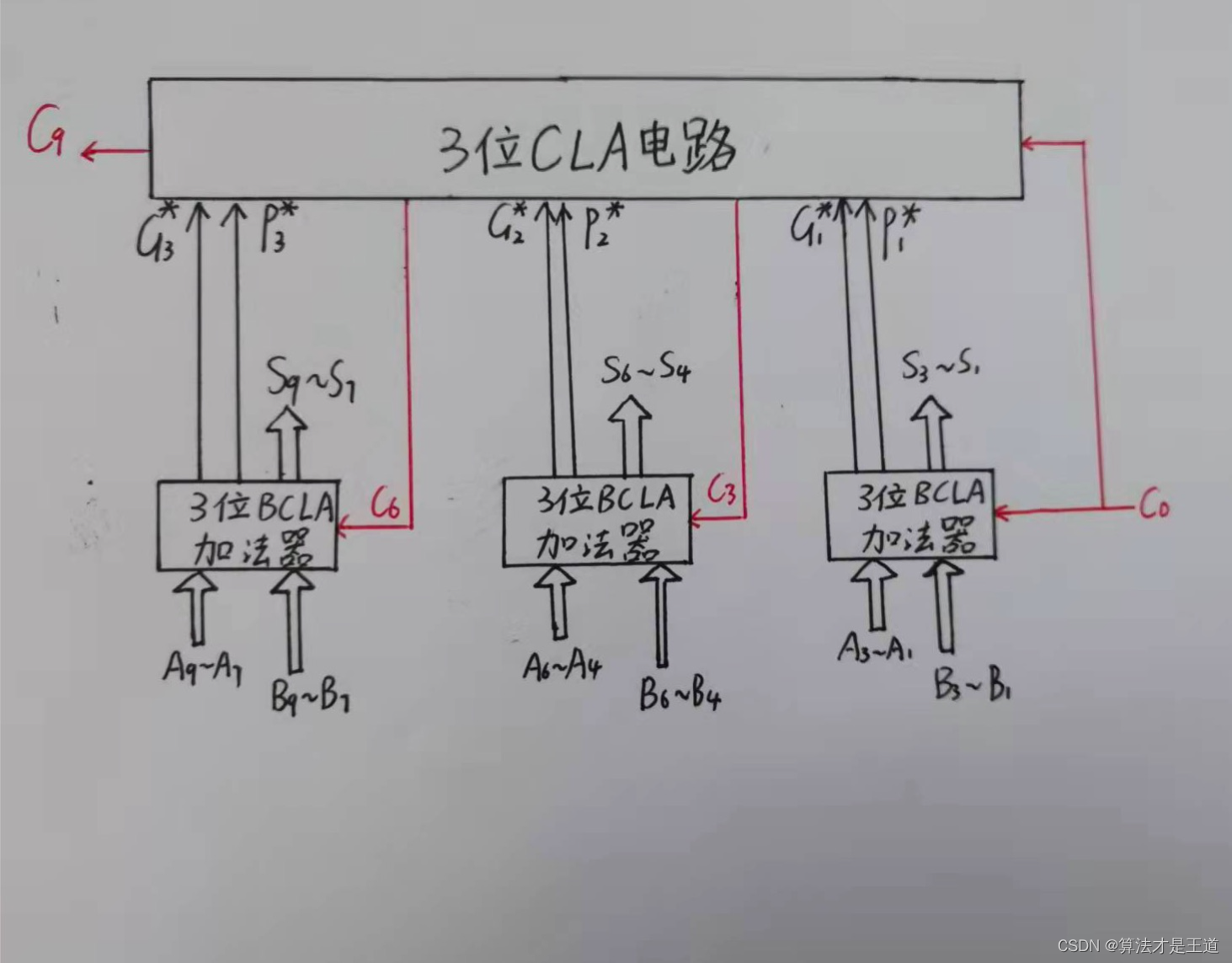

设计一个9位的先行进位加法器,每3位为一组,采用两级先行进位线路。

画图步骤(此步骤只是单纯为了好记)

1、CLA电路、3组3位加法器

2、画Ai、Bi,Gi*,Pi*,Si

3、画Ci

版权声明:本文为e2788666原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。